# Compact Model for Carbon Nanotube Field-Effect Transistors Including Nonidealities and Calibrated With Experimental Data Down to 9-nm Gate Length

Jieying Luo, Student Member, IEEE, Lan Wei, Member, IEEE, Chi-Shuen Lee, Aaron D. Franklin, Member, IEEE, Ximeng Guan, Member, IEEE, Eric Pop, Senior Member, IEEE, Dimitri A. Antoniadis, Fellow, IEEE, and H.-S. Philip Wong, Fellow, IEEE

Abstract—A semianalytical carbon nanotube field-effect transistor (CNFET) model based on the virtual-source model is presented, which includes series resistance, parasitic capacitance, and direct source-to-drain tunneling leakage. The model is calibrated with recent experimental data down to 9-nm gate length. Device performance of 22- to 7-nm technology nodes is analyzed. The results suggest that contact resistance is the key performance limiter for CNFETs; direct source-to-drain tunneling results in significant leakage due to low effective mass in carbon nanotubes and prevents further downscaling of the gate length. The design space that minimizes the gate delay in CNFETs subject to OFF-state leakage current ( $I_{OFF}$ ) constraints is explored. Through the optimization of the length of the gate, contact, and extension regions to balance the parasitic effects, the gate delay can be improved by more than 10% at 11- and 7-nm technology nodes compared with the conventional 0.7× scaling rule, while the OFF-state leakage current remains below  $0.5 \mu A/\mu m$ .

Index Terms—Carbon nanotube (CNT), carbon nanotube field effect transistor (CNFET), contact resistance, direct source-to-drain tunneling.

Manuscript received January 21, 2013; revised April 2, 2013; accepted April 2, 2013. Date of publication May 6, 2013; date of current version May 16, 2013. This work was supported in part by the MSD and the C2S2 Focus Centers, two of six research centers funded under the Focus Center Research Program, a Semiconductor Research Corporation subsidiary, and the member companies of the Stanford Initiative for Nanoscale Materials and Processing. It is additionally supported by IBM through its membership at the Center for Integrated Systems at Stanford. J. Luo and L. Wei are additionally supported by the Stanford Graduate Fellowship. E. Pop has been supported by the NSF CAREER under award ECCS 0954423. The review of this paper was arranged by Editor A. C. Seabaugh.

- J. Luo, C.-S. Lee, and H.-S. P. Wong are with the Department of Electrical Engineering, Stanford University, Stanford, CA 94305 USA (e-mail: ivyluo@stanford.edu; chishuen@stanford.edu; hspwong@stanford.edu).

- L. Wei was with the Microsystems Technology Laboratories, Massachusetts Institute of Technology, Cambridge, MA 02139 USA. She is now with the Altera Corporation, San Jose, CA 95134 USA (e-mail: lwei@altera.com).

- A. D. Franklin is with the IBM T. J. Watson Research Center, Yorktown Heights, NY 10598 USA (e-mail: aaronf@us.ibm.com).

- X. Guan was with the Department of Electrical Engineering, Stanford University, Stanford, CA 94305 USA. He is now with the IBM Semiconductor Research and Development Center, Hopewell Junction, NY 12533 USA (e-mail: xguan@us.ibm.com).

- E. Pop is with the Department of Electrical and Computer Engineering, University of Illinois at Urbana-Champaign, Urbana, IL 61801 USA (e-mail: epop@illinois.edu).

- D. A. Antoniadis is with the Microsystems Technology Laboratories, Massachusetts Institute of Technology, Cambridge, MA 02139 USA (e-mail: daa@mtl.mit.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2013.2258023

#### I. INTRODUCTION

ARBON nanotube field-effect transistors (CNFETs) are among the most promising candidates to replace Si CMOS technology toward the 7-nm node and beyond [1], [2]. Carbon nanotubes (CNTs) provide high carrier velocity, quasiballistic transport, and inherent quasi-one-dimensional (1-D) nanometer-scale (<2 nm) structure. Numerous CNFET demonstrations have been made recently [3]: highly aligned CNTs grown on full wafer scale [4], complex logic gates [5], [6], stable complementary n- and p-channel transistors on the same chip [7]-[10], and operation at 0.4-V power supply [11], and CNFETs have been shown to outperform the best Si transistors for low-power applications [12]. These device/technology and circuit design advances [13] further strengthen the leading position of CNFETs as a promising candidate to complement Si CMOS in future technology nodes.

A computationally efficient compact model for the CNFET is indispensible for the design of large-scale circuit and for estimating and optimizing the performance of CNFET circuits for future technology nodes. Most published compact models focus on the intrinsic properties of CNFETs [14]-[17], with only a few exceptions accounting for the parasitic capacitances [18]. However, beyond the 22-nm technology node, extrinsic components become important and careful optimization to balance the tradeoffs is required [19], [20]. Tunneling is another obstacle to the advance of transistor scaling. Direct source-to-drain tunneling has been found significant when the gate length is scaled down to sub-10 nm [21]-[23], from both experimental and simulation perspectives. Numerical simulation using the nonequilibrium Green's function (NEGF) formalism [24], [25] provides physically sound means, but is too computationally expensive for device optimization and circuit simulation. Therefore, it is essential to develop a compact CNFET model capturing both the parasitic effects and the tunneling current.

In this paper, we demonstrate a compact CNFET model that is based on the virtual-source (VS) model. The VS model is a semiempirical model applicable to MOSFETs and relies on a large amount of reproducible data to extract empirical parameters such as mobility and inverse subthreshold slope (SS). For emerging devices such as the CNFET,

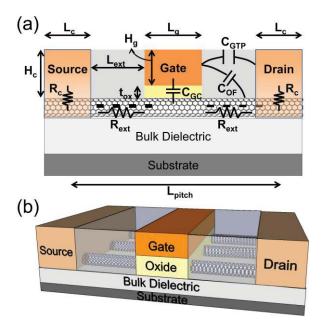

Fig. 1. CNFET structrue with planar top gate and multiple CNTs in the channel. (a) Lengthwise cut view. (b) 3-D view.

it is difficult to obtain large amounts of reliable data, yet there is a strong need for a realistic model to assess their potential for future use. In our proposed model, we relate the empirical parameters, as much as possible, with the device structures such as gate length and contact length to enable projections that reflect changes in the device design, while the other parameters are extracted from a few sets of experimental data. This model captures CNFET's physical properties such as diameter-dependent tunneling and CNT—metal contact resistance, which are important for the purpose of performance benchmarking, projection, and circuit design and optimization.

The VS model is one of the components of this hierarchical model. While each of the constituent components have been published by authors before, the constituent components do not lend themselves to gaining physical insights into how to optimize the CNFET and how to use them for design optimization and circuit simulation. The way the constituent models are put gather is the main contribution of this paper.

This paper is organized as follows. In Section II, each level of the model is described. Calibration with experimental data from 300-nm down to 9-nm gate length is presented in Section III. Based on the parameters extracted from Section III, the performances of 22- to 7-nm technology nodes are projected and the challenges related to parasitic effects and direct tunneling are highlighted in Section IV. Finally, Section V illustrates the use of the model for device the optimization of CNFETs at the 11- and 7-nm technology nodes.

#### II. CNFET MODEL

Fig. 1 illustrates the modeled device structure. It is a planar top-gated CNFET with an undoped CNT channel and ungated,

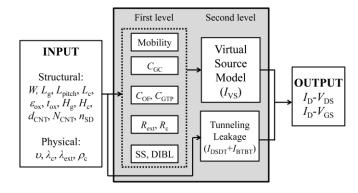

Fig. 2. Hierarchical structure of the CNFET model. The inputs are the design and physical parameters labeled in Fig. 1(a).

highly-doped source/drain (S/D) extensions. A single CNFET contains multiple CNTs in parallel within the channel to boost the drive current. The ungated S/D extensions can offset the gate electrode from the S/D contact plugs and reduce the parasitic capacitance [27]. Present experimental CNFETs often employ a back gate with gate-to-S/D overlap [28], [29] or undoped (not intentionally doped), underlapped, and ungated extension regions [30], because a stable and well-controlled CNT doping technology is not yet available. However, it is well known that the structure in Fig. 1 can achieve better device performance with CMOS-compatible fabrication [31], [32] due to its effectiveness in reducing parasitic capacitances.

The model takes the CNFET structure design and physical parameters as inputs. The design parameters include the device pitch  $(L_{pitch})$ , length of the gate  $(L_g)$  and the contact  $(L_c)$ , the gate width (W), the dielectric constant  $(\varepsilon_{\rm ox})$  and thickness  $(t_{\rm ox})$  of the gate oxide, the height of the gate  $(H_g)$  and the S/D contact plugs  $(H_c)$ , the CNT diameter ( $d_{\text{CNT}}$ ), the CNT density ( $N_{\text{CNT}}$ ), and the doping density at the extensions  $(n_{SD})$ .  $d_{CNT}$  is an intrinsic physical property of the CNT. The bandgap of the semiconducting CNT can be approximated by  $E_g \approx 2\gamma a_{\rm CC}/d_{\rm CNT}$  [33], where  $a_{\rm CC} \approx 1.42$  Å is the length of carbon–carbon bonds, and  $\gamma \approx 3$  eV is the nearest-neighbor overlap energy that is used as a fitting parameter in the tight-binding method. The physical parameters are the velocity at the VS (v), the carrier mean free paths in the CNTs (denoted by  $\lambda_c$  and  $\lambda_{ext}$ for the parts under the S/D metal contacts and extensions, respectively), and the specific contact resistance of the metal-CNT contact  $(\rho_c)$ , all of which can be extracted from the experiments.

The hierarchical structure of the model is shown in Fig. 2. The first level is composed of models for the intrinsic and extrinsic components including the mobility, gate-to-channel capacitance, series resistances, parasitic capacitances, SS and drain-induced-barrier-lowering (DIBL) coefficient. The second level has two models: 1) the VS model utilizing the outputs of the first level to generate the thermionic emission current  $I_{\text{VS}}$  and 2) a semianalytical model for the tunneling current  $I_{\text{TUNNEL}}$ . The final output drain current is given by  $I_{\text{D}} = I_{\text{VS}} + I_{\text{TUNNEL}}$ . The details of each part are described below.

### A. Models for Intrinsic and Extrinsic Components

1) Mobility ( $\mu$ ): We employ an experimentally corroborated physics-based mobility model for CNTs that applies both to the diffusive and quasi-ballistic transport regimes [34], taking into account the acoustic phonon (AP) and optical phonon (OP) scattering.

$$\mu = \frac{4qL_g}{hn} \sum_{i} \int_0^\infty \frac{\lambda(E)}{L_g + \lambda(E)} \left( -\frac{\partial f}{\partial E} \right) dE$$

(1a)

$$\frac{1}{\lambda} = \frac{1}{\lambda_{\text{AP}}(E, T)} + \frac{1 - f(E + \hbar\omega_{\text{OP}})}{\lambda_{\text{OP,abs}}(E, T)} + \frac{1 - f(E - \hbar\omega_{\text{OP}})}{\lambda_{\text{OP,ems}}(E, T)}$$

(1b)

where n is the charge density, f is the Fermi–Dirac distribution, i is the summation index over the first and second subbands,  $\hbar\omega_{\rm OP}\approx 0.18$  eV is the OP energy,  $\lambda_{\rm AP}$ ,  $\lambda_{\rm OP,abs}$ , and  $\lambda_{\rm OP,ems}$  are mean free paths for AP scattering, OP absorption, and emission, respectively, which depend on the energy and the temperature. Low-field mobility at a charge density of  $n=0.01~{\rm nm}^{-1}$  is used in the model. Because  $\lambda_{\rm AP}$ ,  $\lambda_{\rm OP,abs}$ , and  $\lambda_{\rm OP,ems}$  are proportional to  $d_{\rm CNT}$  [34], [35],  $\mu$  increases when  $d_{\rm CNT}$  increases.

- 2) Gate-to-Channel Capacitance ( $C_{\rm GC}$ ): Analytical expression of  $C_{\rm GC}$ , including the screening effects between multiple CNTs under a single planar gate, has been derived in [36], and the details are presented in the Appendix.  $C_{\rm GC}$  is one of the most important factors determining the drive current because it is proportional to the amount of carriers induced by the gate electric field.

- 3) Series Resistances ( $R_S$ ): The series resistance  $R_s$  has two components, one being the resistance of the ungated S/D extensions ( $R_{ext}$ ) [37].

$$R_{\text{ext}} = L_{\text{ext}}/(\lambda_{\text{ext}}G_{1\text{D}}), \quad G_{1\text{D}} = \frac{4q^2}{h} \frac{e^{\Delta/kT}}{1 + e^{\Delta/kT}}$$

(2)

where  $\Delta \equiv E_{\rm FS} - E_{\rm C}$  ( $E_{\rm V}$ ) for n-type (p-type) CNFETs, and  $E_{\rm FS}$  is the Fermi level at the S/D extensions related to the doping density  $n_{\rm SD}$ . When the CNTs are highly doped,  $1/G_{\rm 1D} \approx 4q^2/h \equiv R_Q = 6.45~{\rm k}\Omega$  is the quantum resistance for CNTs with two-band degeneracy. The other component is the contact resistance ( $R_c$ ) between the CNTs and metal contacts [38].

$$R_c = \sqrt{\frac{1}{4} + \frac{\rho_C}{\lambda_c R_Q}} R_Q \coth\left(\sqrt{\frac{R_Q}{\rho_c \lambda_c} + \frac{R_Q^2}{4\rho_c^2}} L_c\right)$$

(3)

where  $\rho_c$  is equivalent to the reciprocal of the contact conductance  $g_c$  in [38]. Note that  $\rho_c$  here is different from the conventional contact resistivity for Si MOSFETs. In the transmission line model,  $1/\rho_c$  is the conductance per unit length along the CNT. When  $L_c$  is smaller than the transfer length,  $R_c \approx R_Q/2 + \rho_c/L_c$ . The total parasitic resistance for a single CNT is the sum of these two, that is,  $R_s = R_{\rm ext} + R_c$ .

4) Parasitic Capacitances ( $C_P$ ): The parasitic capacitance of a CNFET consists of two components: the outer-fringe capacitance ( $C_{OF}$ ) between the gate and the CNTs in the S/D extensions, and the gate-to-plug capacitance ( $C_{GTP}$ ) between the gate and the S/D contact plug [36]. The details are described in the Appendix.

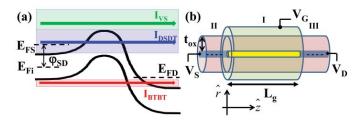

Fig. 3. (a) Band diagram to illustrate the tunneling current. (b) Gate-all-around cylindrical structure used to model the potential profile. The source and drain extensions are highly doped.

5) SS and DIBL Coefficient  $\delta$ : SS and DIBL coefficient  $\delta$  are calculated by the ratio of the capacitances coupling to the VS in the channel [39].

$$SS = \ln\left(10\right) \frac{kT}{q} \left(\frac{C_{GC} + C_S + C_D}{C_{GC}}\right) \tag{4a}$$

$$\delta = C_{\rm D}/(C_{\rm GC} + C_{\rm S} + C_{\rm D}) \tag{4b}$$

where  $C_{\rm GC}$ ,  $C_{\rm S}$ , and  $C_{\rm D}$  are capacitances coupling from the gate, source, and drain to the channel, respectively. The models of  $C_{\rm S}$  and  $C_{\rm D}$  are verified by Maxwell 3-D [40], and the details are in the Appendix. This model can be easily applied to other structures as long as appropriate models for  $C_{\rm GC}$ ,  $C_{\rm S}$ , and  $C_{\rm D}$  are used.

#### B. VS Model

The VS model is a semiempirical model applicable to short-channel MOSFETs in all regions of operation, from ballistic transport to diffusive velocity saturation [26]. The inputs of the VS model include: v,  $\mu$ , SS,  $\delta$ ,  $R_s$ , and  $C_p$ . v can be extracted from experimental data and will be discussed in Section III.  $\mu$ , SS,  $\delta$ ,  $R_s$ , and  $C_p$  are calculated from the models in Section II-A.

There are two fitting parameters in the VS model,  $\alpha$  and  $\beta$ , which model the channel charge from weak to strong inversion and the transition from linear to saturation region, respectively. As a start, the values  $\alpha = 3.5$  and  $\beta = 1.4$ , borrowed from Si MOSFETs, are used. More experiments are required to determine the specific  $\alpha$  and  $\beta$  for CNFETs.

With all the inputs of the VS model calculated appropriately in Section II-A and the two fitting parameters empirically set, the VS current can be generated.

# C. Tunneling Leakage Current

Two tunneling mechanisms are modeled as illustrated in Fig. 3(a): direct source-to-drain tunneling current ( $I_{DSDT}$ ) from the source conduction band (CB) into the drain CB, and the band-to-band tunneling (BTBT) from the source valence band into the drain CB.

To evaluate the tunneling probability, knowing the band profile along the channel is indispensable. In this paper, we employ a gate-all-around (GAA) cylindrical structure as illustrated in Fig. 3(b) to derive a semianalytical model for the band profile as an estimation of the impact of  $I_{DSDT}$ , because a planar CNFET structure like that in Fig. 1 has no

analytical solution. The CNT is divided into the channel region and extension regions denoted by I, II, and III in Fig. 3(b). In the subthreshold region, mobile charge is negligible and the surface potential in region I is approximated as the solution to the Laplace's equation in cylindrical coordinates [41].

$$\phi_{\rm I}(z) \approx J_0 (\xi_0) \left[ C_1 \exp(z/\Lambda) + C_2 \exp(-z/\Lambda) \right] + V_{\rm CNT}$$

$$C_2 = \frac{(V_{\rm bi} - V_{\rm CNT}) \left( e^{L_g/\Lambda} - 1 \right) - V_{\rm DS}}{2J_0 (\xi_0) \sinh\left( L_g/\Lambda \right)}$$

$$C_1 = \frac{V_{\rm bi} - V_{\rm CNT}}{J_0 (\xi_0)} - C_2$$

$$\frac{Y_0' (\xi_0)}{J_0' (\xi_0)} = \kappa_e \frac{Y_0 (\xi_0)}{J_0 (\xi_0)} + (1 - \kappa_e) \frac{Y_0 (\xi_0 + t_{\rm ox}/\Lambda)}{J_0 (\xi_0 + t_{\rm ox}/\Lambda)}$$

(5b)

where  $J_0$  and  $Y_0$  are Bessel functions of the first and second kinds, respectively,  $\xi_0 = d_{\rm CNT}/2\Lambda$ ,  $\Lambda$  is the scale length given in (5b) to satisfy the continuity of perpendicular component of electric field at the CNT/dielectric interface.  $\kappa_e = \varepsilon_{\rm CNT}/\varepsilon_{\rm OX}$  is the ratio of the dielectric constant of CNT to the gate oxide. In this paper,  $\varepsilon_{\rm CNT} = 1$  and  $\varepsilon_{\rm OX} = 16$  are chosen.  $C_1$  and  $C_2$  are coefficients determined by the boundary conditions  $\phi_{\rm I}(0) = V_{bi}$  and  $\phi_{\rm I}(L_g) = V_{bi} + V_{\rm DS}$  and  $V_{bi}$  is the built-in potential proportional to  $E_{\rm Fi} - E_{\rm FS}$ . The reference point is chosen at  $E_{\rm FS} = 0$  so that the intrinsic Fermi level is equal to  $-q\phi_{\rm I}(z)$ . To account for the mobile charge induced by the gate,  $V_{\rm CNT}$  is introduced as the actual voltage dropped on CNTs satisfying

$$V_{\text{GS}} - V_{\text{FB}} = qn/C_{\text{ox}} + V_{\text{CNT}}$$

$$n = n_i \exp\left[\frac{-\phi_I (z_{\text{max}})}{kT/q}\right], \quad z_{\text{max}} = \frac{\Lambda}{2} \ln \frac{C_2}{C_1}$$

$$n_i = 4\sqrt{kT \cdot E_g}/(3\sqrt{\pi}a_{\text{CC}}\gamma) \cdot \exp\left(-E_g/(2kT)\right)$$

$$C_{\text{ox}} = 2\pi \varepsilon_{\text{ox}}/\ln\left[(d_{\text{CNT}} + 2t_{\text{ox}})/d_{\text{CNT}}\right]$$

(6)

where  $V_{\rm GS}$  and  $V_{\rm FB}$  are the gate and flat-band voltages, respectively, and  $z_{\rm max}$  corresponds to the position of the band maximum in the channel. Derivation of the CNT intrinsic carrier density  $n_i$  was elucidated in [42].

At the junctions of the channel and the S/D extensions, the electric field does not terminate abruptly but penetrates into the extensions, leading to a tail in the band profile [43] and affects  $I_{DSDT}$ . In this paper, we use an exponential function to phenomenologically model the descending potential in the S/D extensions.

$$\phi_{II}(z) = \left[\phi_{I}(0) - \frac{\varphi_{SD}}{q}\right] \exp\left[\frac{\partial \phi_{I}(0)/\partial z}{\phi_{I}(0) - \phi_{S}}z\right] + \frac{\varphi_{SD}}{q} \quad (7a)$$

$$\phi_{III}(z) = \left[\phi_{I}(L_{G}) - \frac{\varphi_{SD}}{q} - V_{DS}\right]$$

$$\exp\left[\frac{\partial \phi_{I}(L_{g})/\partial z}{\phi_{I}(L_{g}) - \varphi_{SD}/q - V_{DS}}z\right] + \frac{\varphi_{SD}}{q} + V_{DS} \quad (7b)$$

where  $\varphi_{SD} = E_{FS} - E_{Fi}$ , and  $E_{Fi}$  is the intrinsic Fermi level. Equation (8) links the band profile in regions I, II, and III smoothly.

Given the potential profile,  $I_{DSDT}$  in the ballistic transport regime can be evaluated as [44]

$$I_{\text{DSDT}} = \frac{4q}{h} \int_{E_g/2 - q_{\text{SD}}}^{E_g/2 - q_{\text{Cmax}}} T(E) [f(E, E_{\text{FS}}) - f(E, E_{\text{FS}} - q_{\text{VDS}})] dE$$

(8)

where the prefactor of four arises from the double degeneracy of the first sub-band and electron spin. The tunneling probability T(E) is calculated by the transfer matrix method [45] that takes the band profiles calculated in (6) and (8) as inputs. More details of the calculation of tunneling probability and analytical expressions of band profile will be discussed in a later publication.

BTBT current ( $I_{BTBT}$ ) is calculated by the Wentzel–Kramers–Brillouin (WKB) method using the triangular barrier approximation [46].

$$I_{\text{BTBT}} \approx \frac{4q}{h}kT \cdot T_{\text{WKB}} \left[ \ln \frac{e^{(E+qV_{\text{DS}})/kT} + 1}{e^{E/kT} + 1} \right]_{-qV_{\text{DS}} - \varphi_{\text{SD}} + E_g/2}^{-\varphi_{\text{SD}} - E_g/2}$$

$$T_{\text{WKB}} \approx \exp \left[ -\frac{\pi}{4} \cdot \frac{E_g^2}{\hbar v_{\text{F}} q F} \right]$$

(9)

where  $v_F \sim 10^6$  m/s is the Fermi velocity, F is the electric field in the junction at the drain calculated from  $\partial \phi / \partial z$  in (7b).  $T_{\rm WKB}$  in (9) is a result of the hyperbolic band structure of CNTs and is different from the bulk semiconductors such as silicon or germanium. It is worth noting that phonon-assisted tunneling [47] is not yet included in the model and remains a subject for future works. Therefore, only when  $V_{\rm DS} > E_g$ , can  $I_{\rm BTBT}$  be appreciable.

$I_{\rm TUNNEL}$  is simply the sum of  $I_{\rm DSDT}$  and  $I_{\rm BTBT}$  and is superimposed on  $I_{\rm VS}$  obtained in Section II-B by matching the threshold voltage  $(V_{\rm T})$ , which is defined as the  $V_{\rm GS}$  for which the derivative of transconductance  $\partial g_m/\partial V_{\rm GS}$  is a maximum [48]. Although the device configuration used to derive the tunneling leakage is different from the planar structure in Fig. 1, it provides an efficient and physically logical means to capture the impact of tunneling for the scaled CNFETs.

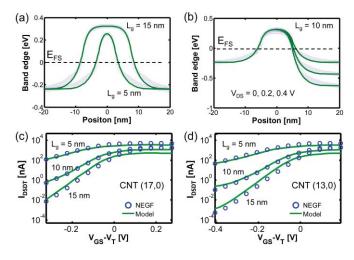

The modeled  $I_{DSDT}$  is compared to an open-source simulator which solves the Poisson and Schrödinger equations self-consistently using the NEGF formalism and calculates the current in ballistic transport regime in CNFETs with a GAA cylindrical geometry and doped S/D extensions [25]. Fig. 4 shows the comparison of the band profile as well as  $I_{DSDT}$  obtained from the model and the NEGF simulation. In Fig. 4(a) and (b), the potential tails in the S/D extensions broaden the tunneling barrier width. Good agreement between the modeled  $I_{DSDT}$  and the numerical simulation is observed when high-k dielectric is used ( $\varepsilon_{OX} > 8$ ) as shown in Fig. 4(c) and (d).

## III. MODEL CALIBRATION WITH EXPERIMENTS

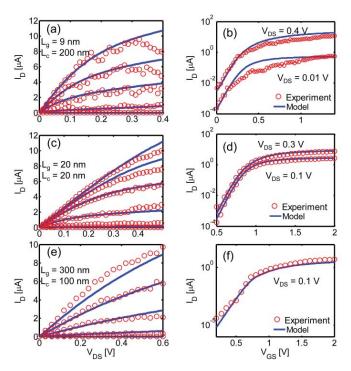

The CNFET model is fitted to the latest experimental I-V characteristics for long-channel ( $L_g=300$  nm and  $L_c=100$  nm) and short-channel ( $L_c=20$  nm,  $L_c=20$  nm and  $L_g=9$  nm, and  $L_c=200$  nm) CNFETs [28], [29].

Fig. 4. Comparison of the band profile and direct source-to-drain tunneling current between the semianalytical model and the numerical NEGF simulation.  $t_{\rm OX}=3$  nm,  $\varepsilon_{\rm OX}=16$ , and the doping density at the S/D extensions  $n_{\rm SD}=1$  nm<sup>-1</sup> are used. (a)  $V_{\rm DS}=0$  V. (b)  $V_{\rm GS}=0$  V. (c) CNT chirality (17, 0) corresponding to  $E_g=0.66$  eV. (d) CNT chirality (13, 0) corresponding to  $E_g=0.86$  eV.  $V_{\rm DS}=0.4$  V for both (c) and (d).

Tunneling model is not included in the calibration, as the tunneling current is not significant in the experimental data.  $d_{\rm CNT} = 1.2 - 1.4$  nm was observed in all the devices. Thus, an average of  $d_{\text{CNT}} = 1.3$  nm is used in the model when fitting to the data, which corresponds to  $E_g \approx 0.66$  eV. The calibrated I-V curves along with the experimental data are shown in Fig. 5. The signs of  $V_{GS}$  and  $V_{DS}$  are flipped over to make the device plots *n*-type-like for convenience. A local bottom gate was utilized to modulate the carriers in the CNTs, which is different from the modeled structure shown in Fig. 1. Thus, the intrinsic capacitance  $C_{GC}$  of the back-gated structure is obtained from TCAD Sentaurus [49] and serves as the input. Because of the device structure difference between the experimental device and the model, SS and DIBL are not calculated from (4) and (5) but remain as fitting parameters. To accommodate the notable hysteresis observed in the experiments, the  $V_{\rm T}$  in the  $I_{\rm D}$ - $V_{\rm DS}$  characteristics is shifted by a constant value ( $\leq 0.2$  V) compared with the  $V_T$  extracted from  $I_D$ – $V_{GS}$  characteristics. Finally, the parasitic resistance is purely the contact resistance, since there are no S/D extensions in the experimental devices.

The VS velocity v, an empirical parameter to the VS model, and  $\rho_c$  and  $\lambda_c$  of the contact resistance model as in (3) are extracted by tuning these parameters to match the experimental data.  $v=3\times 10^5$  m/s,  $\rho_c=420$  k $\Omega$ ·nm, and  $\lambda_c=250$  nm are obtained from the calibration. It is worth noting that the v is proportional to the saturation current at high  $V_{\rm GS}$ , and  $\rho_c$  determines how fast the  $R_c$  increases with the shrinking  $L_c$ . A large  $\rho_c$  leads to large  $R_c$  and less steep slope in the  $I_{\rm D}$ – $V_{\rm DS}$  characteristics. The diameter-normalized contact resistivity is  $\rho_c.d_{\rm CNT}=546$  k $\Omega$ ·nm², a little higher than the one reported in [28]. Because the devices used for calibration have no extension regions,  $\lambda_{\rm ext}$  cannot be extracted and is assumed to be equal to  $\lambda_c$ . When the technology for CNT doping is better developed,  $\lambda_{\rm ext}$  can be characterized more accurately.

Fig. 5. Comparison of  $I_{\rm D}-V_{\rm DS}$  and  $I_{\rm D}-V_{\rm GS}$  between the experiments and the model. (a)  $I_{\rm D}-V_{\rm DS}$  and (b)  $I_{\rm D}-V_{\rm GS}$  for  $L_g=9$  nm and  $L_c=200$  nm. (c)  $I_{\rm D}-V_{\rm DS}$  and (d)  $I_{\rm D}-V_{\rm GS}$  for  $L_g=20$  nm and  $L_c=20$  nm. (e)  $I_{\rm D}-V_{\rm DS}$  and (f)  $I_{\rm D}-V_{\rm GS}$  for  $L_g=300$  nm and  $L_c=100$  nm.

TABLE I

CNFET STRUCTURE PARAMETERS: 22- TO 7-nm NODES

| Technology<br>Node      | 22-nm  | 14-nm | 11-nm | 7-nm  |

|-------------------------|--------|-------|-------|-------|

| L <sub>pitch</sub> [nm] | 80-100 | 56–70 | 40-55 | 30-40 |

| $L_g$ [nm]              | 25-28  | 18-20 | 13-15 | 10-12 |

| $L_c$ [nm]              | 26     | 18    | 12    | 10    |

| EOT [nm]                | 1      | 0.9   | 0.8   | 0.7   |

| $H_g$ [nm]              | 30     | 20    | 20    | 15    |

| W [nm]                  | 160    | 112   | 90    | 63    |

## IV. IMPACT OF PARASITICS AND TUNNELING

With the model validated by experimental data from  $L_g =$ 300 to 9 nm, next, we explore the impact of these nonidealities on the device characteristics of CNFETs for the future technology nodes. Projected device dimensions at each technology node are listed in Table I [50], [51]. The other parameters are: 1)  $n_{SD}$  is assumed to be 1 nm<sup>-1</sup>, corresponding to 0.6% free carriers per carbon atom for the CNTs with diameter  $\sim$ 1.3 nm; 2)  $V_{\rm DD}$  is fixed at 0.6 V as a basis for comparison; 3) CNT density is assumed to be  $N_{\rm CNT} = 250/\mu \rm m$  with equal spacing in order to compete with the Si technology [32]; 4) V<sub>T</sub> is designed to achieve tolerable OFF-state leakage current  $(I_{\rm OFF} \leq 0.5~\mu{\rm A}/\mu{\rm m}$  at  $N_{\rm CNT} = 250/\mu{\rm m}$  defined as  $I_{\rm D}$ at  $V_{GS} = 0$  and  $V_{DS} = V_{DD}$ ; 5) to be concise, the S/D contact plugs are assumed to be as high as the gate, that is,  $H_c = H_g$ . The influence of different  $H_c$ s are discussed in [19] and it is shown that  $C_{GTP}$  is limited by  $H_g$ ; and 6) the material is the bulk dielectric, the spacers have dielectric constant  $\varepsilon = 3.9$ , and a high-k material with  $\varepsilon_{ox} = 16$  is used as the gate oxide. A mean value is used for the analysis if the

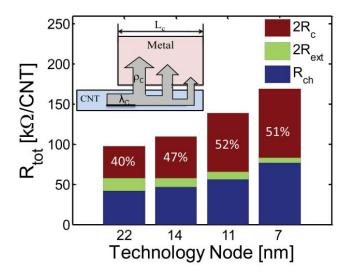

Fig. 6. Composition of the CNFET resistances at different technology nodes.  $R_c$  contributes to most of the resistance. Inset: two conduction mechanisms in the CNT/metal contact: carrier injection from CNT to metal characterized by  $\rho_c$  and carrier transport in the CNT characterized by  $\lambda_c$ .

projected number in Table I is in a certain range, for example,  $L_{\rm pitch} = 0.5 \times (30 + 40) = 35$  nm for the 7-nm technology node. Following the definition in Fig. 1(a),  $L_{\rm ext}$  is equal to  $0.5 \times (L_{\rm pitch} - L_c - L_g)$ . Section IV-A to IV-C examines the impact of series resistance, parasitic capacitance, and tunneling leakage current on the CNFET's performance, as the feature size is scaled down.

## A. Series Resistance

Series resistance increases rapidly with the downscaling of device dimensions and becomes dominant starting from the 11-nm technology node as shown in Fig. 6. The channel resistance is calculated by  $R_{\rm ch}=R_{\rm tot}-2R_{\rm ext}-2R_c$ , where  $R_{\rm tot}$  is the total resistance in the on-state, that is,  $R_{\rm tot}=V_{\rm DD}/I_{\rm ON}$ .  $R_{\rm ch}$  increases with the technology nodes, because higher  $V_{\rm T}$  is required to keep  $I_{\rm OFF}$  low due to increasing SS. Unlike Si MOSFETs in which the parasitic capacitance is the limiting factor for advanced technology nodes [19], today's CNFETs are more limited by the CNT-to-metal contact resistance [52].

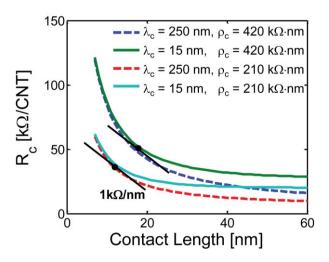

As described in Section II, the series resistance is composed of the extension resistance  $R_{\text{ext}}$  and the contact resistance  $R_c$ .  $R_{\rm ext}$  is proportional to the ratio of  $L_{\rm ext}$  to the mean free path  $\lambda_{\rm ext}$ , while the contact resistance has a more complex dependence on the physical parameters and the contact length. The physics that determine the resistance of the CNT/metal contact are: 1) carrier injection from CNT to metal, whose rate is proportional to  $1/\rho_c$ , and (2) carrier transport in the CNTs that are covered by the contact metal, which is characterized by  $\lambda_c$ . In the quasi-ballistic regime,  $1/\lambda_c$  is the scattering probability in CNTs per unit length and is highly dependent on the CNT growth and doping conditions. A wide range of  $\lambda_c$  from 20 to 380 nm has been reported in [38] and [53]. A pessimistic estimation of  $\lambda_c = 15$  nm is used in the following analysis. Because of the distributed nature of the CNT-metal interface,  $R_c$  decreases with a hyperbolic cotangent dependence on  $L_c$  [54], as shown in Fig. 7, with

Fig. 7.  $R_c$  versus  $L_c$  at different  $\lambda_c$  and  $\rho_c$ . When  $L_c < 20$  nm,  $R_c$  increases dramatically as  $L_c$  decreases. The starting point of the "short contact regime" is marked at where the  $dR_c/dL_c=1$  k $\Omega$ /nm.

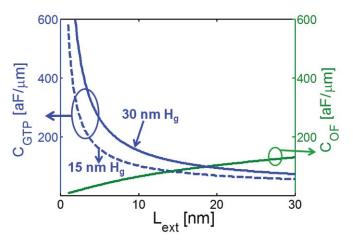

Fig. 8. Parasitic capacitances  $C_{\rm GTP}$  and  $C_{\rm OF}$  versus  $L_{\rm ext}$ . The total parasitic capacitance increases rapidly when  $L_{\rm ext} < 10$  nm. Lowering the height of the gate and contact plugs can reduce  $C_{\rm GTP}$  and improve the performance.

the lower bound equal to the quantum resistance. The first derivative of  $R_c$  with respect to  $L_c$  reaches 1 k $\Omega$ /nm when  $L_c < 20$  nm, demarcating the region where the  $R_c$  starts to shoot up. This is a manifestation of the "short contact regime" where  $R_c$  starts to increase drastically with decreasing  $L_c$ . At 7-nm node with  $L_c = 10$  nm,  $\rho_c$  has to be reduced to 120 k $\Omega$ ·nm in order to achieve  $2R_c < 0.3R_{\rm tot}$ , around 30% of its original value.

# B. Parasitic Capacitance

The ratio of intrinsic capacitance  $C_{\rm GC}$  to the parasitic capacitances ( $C_{\rm OF}+C_{\rm GTP}$ ) decreases from 69% to 60% when scaling from 22-nm node to 7-nm node. Parasitic capacitances impose extra burdens on the device, which not only slow down the switching but also raise the dynamic power consumption. Both capacitances  $C_{\rm OF}$  and  $C_{\rm GTP}$  are functions of  $L_{\rm ext}$  as shown in Fig. 8. As  $L_{\rm ext}$  is shortened,  $C_{\rm GTP}$  increases reciprocally due to stronger gate-to-plug coupling, while  $C_{\rm OF}$  decreases proportionally with  $L_{\rm ext}$ .  $C_{\rm GTP}$  and  $C_{\rm OF}$  intersect around  $L_{\rm ext}=20$  nm at  $H_g=30$  nm. Beyond

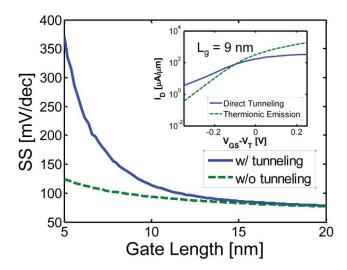

Fig. 9. Inverse subthreshold slope versus gate length. The inset shows the dominance of direct source-to-drain tunneling current in subthreshold region resulting in severe degradation in SS when  $L_{\rm g} < 10$  nm.

this point toward the left,  $C_{\rm GTP}$  dominates, and the total parasitic capacitance increases drastically. Reduction in  $H_g$  can effectively reduce  $C_{\rm GTP}$  and push the intersection of  $C_{\rm GTP}$  and  $C_{\rm OF}$  toward the left allowing further scaling of  $L_{\rm ext}$ . Another benefit of shortening  $L_{\rm ext}$  is to reduce one of the series resistances  $R_{\rm ext}$ . Therefore, there is a tradeoff between parasitic capacitance and series resistance.

# C. Tunneling Leakage Current

Direct source-to-drain tunneling becomes significant when the gate length is very short. As shown in the inset of Fig. 9,  $I_{DSDT}$  dominates over thermionic emission current when the gate length is scaled down to 9 nm and beyond. SS is thus deteriorated with decreasing  $L_g$ . Note that the calculation of  $I_{DSDT}$  in Fig. 9 is based on the GAA cylindrical structure. Whether direct source-to-drain tunneling was appreciable in [29] needs to be further investigated. It has been reported that the metal/CNT contacts also play an important role in the I-V characteristics and affect the SS because the contacts are modulated by the bottom gate [55]. Temperature-dependent measurements might be helpful to elucidate the impact of tunneling leakage current [23].

On the other hand, BTBT occurs when the drain bias  $(V_{\rm DS})$  is larger than the bandgap or the barrier is raised so high by the gate voltage that the valence band in the channel is lifted above the CB at the source. To avoid BTBT, CNTs with smaller diameters are preferred due to larger bandgap as well as lower tunneling probability.

## V. DESIGN SPACE AND STRUCTURE OPTIMIZATION

The primary driver for technology scaling is to reduce cost by shrinking the device pitch  $L_{\rm pitch}$ , which is equal to  $(L_c + 2L_{\rm ext} + L_g)$ . The effects of scaling the individual components have been discussed in Section IV: parasitic resistances, capacitances, and tunneling leakage current increase drastically as  $L_c$ ,  $L_{\rm ext}$ , and  $L_g$  are scaled down, respectively.

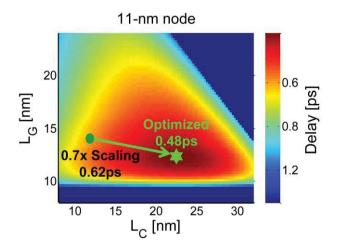

Fig. 10. Optimization at the 11-nm node ( $L_{\rm pitch} = 47.5$  nm). The dark blue regions represent the forbidden designs due to intolerable  $I_{\rm OFF}$  (>0.5  $\mu$ A/ $\mu$ m) or  $L_{\rm ext} < 1$  nm. The delay can be greatly reduced by increasing  $L_c$  (or reducing  $R_c$ ).

It is essential to investigate the tradeoffs between them. In this section, we optimize the ratio of  $L_c$ ,  $L_{\text{ext}}$ , and  $L_g$  with fixed  $L_{\text{pitch}}$  for the 11- and the 7-nm technology node to minimize the gate delay as a demonstration of the model's capability. As a metric for the device performance, the gate delay is defined as  $\tau = C_{\rm IN} V_{\rm DD} / I_{\rm ON}$ , where  $C_{\rm IN} = C_{\rm GC} + C_{\rm GS} +$  $2C_{\rm GD} = C_{\rm GC} + 3(C_{\rm OF} + C_{\rm GTP})$  including the Miller effect. The threshold voltage  $V_{\rm T}$  is determined by maximizing  $I_{\rm ON}$  under the constraint of  $I_{\text{OFF}} \leq 0.5 \ \mu\text{A}/\mu\text{m}$  at  $N_{\text{CNT}} = 250/\mu\text{m}$ . Using this model, one can, for example, explore the interaction between the nanotube diameter and the leakage current; the interplay between the contact resistivity, contact length, and device pitch; the selection of the proper work function for the gate electrode; and the choice of the power supply voltage. These explorations will be part of a future study to examine the energy-delay tradeoffs for CNFET device/circuit co-optimization.

The CNFET dimensions can be found in Table I.  $L_{pitch}$  is restrained at 47.5 nm for the 11-nm node and 35 nm for the 7-nm node. The optimization result and the explored design space for the 11-nm node is shown in Fig. 10. The dark blue regions represent the forbidden designs due to  $I_{OFF}$  constraints  $(I_{\rm OFF} > 0.5 \ \mu {\rm A}/\mu {\rm m})$  or impractical device structure  $(L_{\rm ext} <$ 1 nm). Compared with conventional  $0.7 \times$  scaling rules,  $\tau$  is improved from 0.62 to 0.48 ps for the 11-nm node after the optimization of the ratio of the gate, contact, and extension lengths. For 7-nm node,  $\tau$  is improved from 0.63 to 0.55 ps (explored design space is not shown here). Note that the optimized  $L_c$  is much larger than its original value  $(L_c = 12-23 \text{ nm for the } 11\text{-nm node and } L_c = 10-15 \text{ nm}$ for the 7-nm node), indicating the significance of reducing contact resistances. Assuming that  $\rho_c$  could be reduced by half (420–210 k $\Omega$ ·nm), the optimized  $\tau$  for the 7-nm node would be further reduced from 0.55 to 0.42 ps.

The major obstacle for  $L_g$  scaling is direct source-to-drain tunneling leakage that prevents  $L_g$  from scaling below 10 nm. Employing CNTs with a smaller diameter in a conventional CNFET can reduce the tunneling probability due to a larger bandgap at the cost of increasing effective mass. Constraint of

$L_g$  scaling would be more rigorous when the process variation is included, and can also be evaluated by the model and alleviated by a careful design. Another information from the optimization of the 11- and 7-nm nodes is that the minimum gate delay is increased from the 11-nm node to the 7-nm node, contradicting the traditional Dennard-scaling expectation [56]. This occurs mainly because the decrease in the contact length greatly raises the contact resistance and reduces the drive current.

#### VI. CONCLUSION

In this paper, we introduced a compact, physical, and intuitive CNFET model capturing both intrinsic and extrinsic device properties, and the model could be implemented in SPICE or VerilogA. The model was calibrated with the latest experimental results from 300-nm down to 9-nm gate lengths. Based on the GAA cylindrical configuration, the irregular potential profile along the channel was modeled semianalytically, providing an efficient path to study the impact of the tunneling leakage current in the ultrascaled devices. Through careful optimization of the device structure, made possible by the use of this compact model, the impact of the extrinsic components could be alleviated, and the projected gate delay could be improved by more than 20%. From the exploration of the design space, we observed that: 1) contact resistance is the key limiter of the CNFET performance. Substantial improvement in delay can be achieved if  $\rho_c$  is reduced, showing the importance of improving the CNT-metal interface and 2) direct source-to-drain tunneling limits the downscaling of  $L_g$ . This result is believed to be universal in all kinds of FETs suggesting further study in material and device structure to minimize the tunneling current.

#### APPENDIX

The intrinsic and extrinsic capacitances are derived in [36]. The gate-to-channel capacitance  $C_{\rm GC}$  including screening effects between multiple CNTs under a single planar gate is as shown in (A.1), where  $C_{\rm GC\_INF}$ ,  $C_{\rm GC\_E}$ , and  $C_{\rm GC\_M}$  are  $C_{\rm GC}$  for single CNT and for CNTs at the edge and in the middle of the CNT array, respectively;  $C_{\rm GC\_SR}$  is the equivalent series capacitance due to channel screening; s is CNT pitch;  $k_1$  and  $k_2$  are the relative permittivity of the oxide and substrate, respectively;  $\varepsilon_0$  is the vacuum permittivity; r is the radius of CNT; and h is the distance between the center of CNT and the gate.

$$\begin{split} C_{\text{GC\_E}} &= C_{\text{GC\_INF}} \cdot C_{\text{GC\_SR}} / (C_{\text{GC\_INF}} + C_{\text{GC\_SR}}) \\ C_{\text{GC\_M}} &= 2C_{\text{GC\_E}} - C_{\text{GC\_INF}} \\ C_{\text{GC\_SR}} \\ &= \frac{4\pi \, k_1 \varepsilon_0 L_g}{\ln \left[ \frac{s^2 + 2(h - r)(h + \sqrt{h^2 - r^2})}{s^2 + 2(h - r)(h - \sqrt{h^2 - r^2})} \right] + \lambda_1 \ln \left[ \frac{(h + 2r)^2 + s^2}{9r^2 + s^2} \right] \tanh \left( \frac{h + r}{s - 2r} \right)} \\ C_{\text{GC\_INF}} &= \frac{4\pi \, k_1 \varepsilon_0 L_g}{\cosh^{-1} \left[ (t_{\text{OX}} + r) / r \right] + \lambda_1 \ln \left[ (h + 2r) / 3r \right]} \\ \lambda_1 &= \frac{k_1 - k_2}{k_1 + k_2} \end{split} \tag{A.1}$$

The outer-fringe capacitance (*C*<sub>OF</sub>) between the gate and CNTs in the S/D extensions can be modeled as

$$C_{\text{OF\_INF}} = \pi k_2 \varepsilon_0 L_{\text{ext}} / \cosh^{-1} \left( \sqrt{4h^2 + (0.56L_{\text{ext}})^2} / 2r \right)$$

$$C_{\text{OF\_E}} = \pi k_2 \varepsilon_0 L_{\text{ext}} / \ln \left[ \sqrt{4h^2 + (0.56L_{\text{ext}})^2 + s^2} / s \right]$$

$$+ C_{\text{OF\_INF}} / \eta_1$$

$$C_{\text{OF\_M}} = (2\alpha / \eta_1) C_{\text{OF\_E}} + (1 - 2\alpha / \eta_1) C_{\text{OF\_INF}}$$

$$\eta_1 = \exp \left( \frac{\sqrt{N_{\text{CNT}}^2 - 2N_{\text{CNT}}} + N_{\text{CNT}} - 2}{\tau_1 N_{\text{CNT}}} \right)$$

$$\alpha = \exp \left( \frac{N_{\text{CNT}} - 3}{\tau_2 N_{\text{CNT}}} \right)$$

(A.2)

where  $C_{\text{OF\_INF}}$ ,  $C_{\text{OF,E}}$ , and  $C_{\text{OF,M}}$  are  $C_{\text{OF}}$  for single CNT and for CNTs at the edge and in the middle of the CNT array, respectively.  $\tau_1$  and  $\tau_2$  are empirically set as 2.5 and 2, respectively.

The gate-to-plug capacitance ( $C_{\text{GTP}}$ ) between the gate and the S/D contact plug is ( $\alpha_{\text{GTP\_SR}}$  is empirically set as 0.7).

$$C_{\text{GTP}} = \frac{k_2 \varepsilon_0 H_g W}{L_{\text{ext}}} + \frac{\alpha_{\text{GTP\_SR}} \pi k_2 \varepsilon_0 W}{\ln[2\pi (L_{\text{ext}} + L_g)/(2L_g + \tau_{\text{BK}} H_g)]}$$

$$\tau_{\text{BK}} = \exp\left(2 - 2\sqrt{1 + 2(H_g + L_g)/L_{\text{ext}}}\right). \tag{A.3}$$

The capacitances coupling from the source  $(C_S)$  and drain  $(C_D)$  to the channel are modeled by conformal mapping [39].

$$C_{\rm S} + C_{\rm D} = (\pi/(2u) - 1) C_{\rm GC}$$

$$u = \cos^{-1}(((a - (a^2 - 4)^{0.5})/2)^{0.5})$$

$$a = 2 + b(L_g/2t_{\rm ox})^2$$

$$b = 1.3 - 3.6 \exp(-L_g/1.4d_{\rm CNT}). \tag{A.4}$$

The coefficients in (A.4) are determined by fitting to the numerical simulation results done by Maxwell 3-D [40]. For a CNFET with single CNT,  $C_S/C_D = 3.4$  is extracted empirically.

# ACKNOWLEDGMENT

The authors would like to thank Prof. S. Mitra (Stanford), Dr. D. Frank (IBM), and Dr. W. Haensch (IBM) for useful discussions and help.

## REFERENCES

- [1] R. Chau, S. Datta, M. Doczy, B. Doyle, B. Jin, J. Kavalieros, A. Majumdar, M. Metz, and M. Radosavljevic, "Benchmarking nanotechnology for high-performance and low-power logic transistor applications," *IEEE Trans. Nanotechnol.*, vol. 4, no. 2, pp. 153–158, Mar. 2005.

- [2] P. Avouris, Z. Chen, and V. Perebeinos, "Carbon-based electronics," Nature Nanotechnol., vol. 2, no. 10, pp. 605–615, Oct. 2007.

- [3] H.-S. P. Wong, S. Mitra, D. Akinwande, C. Beasley, C. Yang, H. Y. Chen, X. Chen, G. Close, J. Deng, A. Hazeghi, J. Liang, A. Lin, L. S. Liyanage, J. Luo, J. Parker, N. Patil, M. Shulaker, H. Wei, L. Wei, and J. Zhang, "Carbon nanotube electronics—Materials, devices, circuits, design, modeling, and performance projection," in *Proc. IEEE Int. Electron Devices Meeting*, Dec. 2011, pp. 23.1.1–23.1.4.

- [4] N. Patil, A. Lin, E. R. Myers, K. Ryu, A. Badmaev, C. Zhou, H.-S. P. Wong, and S. Mitra, "Wafer-scale growth and transfer of aligned single-walled carbon nanotubes," *IEEE Trans. Nanotechnol*, vol. 8, no. 4, pp. 498–504, Jul. 2009.

- [5] N. Patil, A. Lin, J. Zhang, H. Wei, K. Anderson, H.-S. P. Wong, and S. Mitra, "Scalable carbon nanotube computational and storage circuits immune to metallic and mispositioned carbon nanotubes," *IEEE Trans. Nanotechnol*, vol. 10, no. 4, pp. 744–750, Jul. 2011.

- [6] A. Lin, N. Patil, H. Wei, S. Mitra, and H.-S. P. Wong, "ACCNT— A metallic-CNT-tolerant design methodology for carbon-nanotube VLSI: Concepts and experimental demonstration," *IEEE Trans. Electron Devices*, vol. 56, no. 12, pp. 2969–2978, Dec. 2009.

- [7] H. Wei, H.-Y. Chen, L. Liyanage, H.-S. P. Wong, and S. Mitra, "Air-stable technique for fabricating n-type carbon nanotube FETs," in Proc. IEEE Int. Electron Devices Meeting, Dec. 2011, pp. 23.2.1–23.2.4.

- [8] N. Moriyama, Y. Ohno, K. Suzuki, S. Kishimoto, and T. Mizutani, "High-performance top-gate carbon nanotube field-effect transistors and complementary metal-oxide-semiconductor inverters realized by controlling interface charges," *Appl. Phys. Exp.*, vol. 3, no. 10, pp. 105102–105104, Oct. 2010.

- [9] N. Moriyama, Y. Ohno, T. Kitamura, S. Kishimoto, and T. Mizutani, "Change in carrier type in high-k gate carbon nanotube field-effect transistors by interface fixed charges," *Nanotechnology*, vol. 21, no. 16, pp. 165201–165207, Apr. 2010.

- [10] L. Ding, Z. Y. Zhang, S. B. Liang, T. Pei, S. Wang, Y. Li, W. W. Zhou, J. Liu, and L.-M. Peng, "CMOS-based carbon nanotube pass transistor logic integrated circuits," *Nature Commun.*, vol. 3, pp. 677–683, Feb. 2012.

- [11] L. Ding, S. Liang, T. Pei, Z. Zhang, S. Wang, W. Zhou, J. Liu, and L.-M. Peng, "Carbon nanotube based ultra-low voltage integrated circuits: Scaling down to 0.4 V," *Appl. Phy. Lett.*, vol. 100, no. 26, pp. 263116-1–263116-5, Jun. 2012.

- [12] A. D. Franklin, S.-J. Han, G. S. Tulevski, M. Luisier, C. M. Breslin, L. Gignac, M. S. Lundstrom, and W. Haensch, "Sub-10 nm carbon nanotube transistor," in *Proc. IEEE Int. Electron Devices Meeting*, Dec. 2011, pp. 23.7.1–23.7.3.

- [13] J. Zhang, A. Lin, N. Patil, H. Wei, L. Wei, H.-S. P. Wong, and S. Mitra, "Robust Digital VLSI using Carbon Nanotubes," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 31, no. 4, pp. 453–471, Apr. 2012.

- [14] M. Najari, S. Frégonèse, C. Maneux, H. Mnif, N. Masmoudi, and T. Zimmer, "Schottky barrier carbon nanotube transistor: Compact modeling, scaling study, and circuit design applications," *IEEE Trans. Electron Devices*, vol. 58, no. 1, pp. 195–205, Jan. 2011.

- [15] G. Gelao, R. Marani, R. Diana, and A. G. Perri, "A semiempirical SPICE model for *n*-type conventional CNTFETs," *IEEE Trans. Nanotechnol.*, vol. 10, no. 3, pp. 506–512, May 2011.

- [16] S. Sinha, A. Balijepalli, and Y. Cao, "Compact model of carbon nanotube transistor and interconnect," *IEEE Trans. Electron Devices*, vol. 56, no. 10, pp. 2232–2242, Oct. 2009.

- [17] K. Natori, Y. Kimura, and T. Shimizu, "Characteristics of a carbon nanotube field-effect transistor analyzed as a ballistic nanowire fieldeffect transistor," J. Appl. Phys., vol. 97, pp. 034306-1–034306-7, Jan. 2005.

- [18] T. J. Kazmierski, D. Zhou, B. M. Al-Hashimi, and P. Ashburn, "Numerically efficient modeling of CNT transistors with ballistic and nonballistic effects for circuit simulation," *IEEE Trans. Nanotechnol.*, vol. 9, no. 1, pp. 99–107, Jan. 2010.

- [19] L. Wei, J. Deng, L.-W. Chang, K. Kim, C.-T. Chuang, and H.-S. P. Wong, "Selective device structure scaling and parasitic engineering: A way to extend the technology roadmap," *IEEE Trans. Electron Devices*, vol. 56, no. 2, pp. 312–320, Feb. 2009.

- [20] I. Young, "The impact of MOSFET extrinsic R, C parasitics and potential solutions," in *Proc. IEEE Int. Electron Devices Meeting*, Dec. 2011.

- [21] S. Sylvia, H.-H. Park, M. Khayer, K. Alam, G. Klimeck, and R. Lake, "Material selection for minimizing direct tunneling in nanowire transistors," *IEEE Trans. Electron Devices*, vol. 59, no. 8, pp. 2064–2069, Aug. 2012.

- [22] M. Luisier, M. Lundstrom, D. A. Antoniadis, and J. Bokor, "Ultimate device scaling: Intrinsic performance comparisons of carbon-based, InGaAs, and Si field-effect transistors for 5 nm gate length," in *Proc.* IEEE Int. Electron Devices Meeting, Dec. 2011, pp. 11.2.1–11.2.4.

- [23] H. Kawaura, T. Sakamoto, and T. Baba, "Observation of source-to-drain direct tunneling current in 8 nm gate electrically variable shallow junction metal-oxide-semiconductor field-effect transistors," *Appl. Phys. Lett.*, vol. 76, pp. 3810–3812, Apr. 2000.

- [24] G. Fiori and G. Iannaccone, "Three-dimensional simulation of one-dimensional transport in silicon nanowire transitors," *IEEE Trans. Nanotechnol.*, vol. 6, no. 5, pp. 524–529, Sep. 2007.

- [25] G. W. Budima, Y. Gao, X. Wang, S. Koswatta, and M. Lundstrom. (2010). Cylindrical CNT MOSFET Simulator [Online]. Available: http://nanohub.org/resources/moscntr

- [26] A. Khakifirooz, O. M. Nayfeh, and D. Antoniadis, "A simple semiempirical short-channel MOSFET current-voltage model continuous across all regions of operation and employing only physical parameters," *IEEE Trans. Electron Devices*, vol. 56, no. 8, pp. 1674–1680, Aug. 2009.

- [27] L. Wei, J. Deng, and H.-S.P. Wong, "Modeling and performance comparison of 1-D and 2-D devices including parasitic gate capacitance and screening effect," *IEEE Trans. Nanotechnol.*, vol. 7, no. 6, pp. 720–727, Nov. 2008.

- [28] A. D. Franklin and Z. Chen, "Length scaling of carbon nanotube transistors," *Nature Nanotechnol.*, vol. 5, no. 12, pp. 858–862, Nov. 2010.

- [29] A. D. Franklin, M. Luisier, S.-J. Han, G. Tulevski, C. M. Breslin, L. Gignac, M. S. Lundstrom, and W. Haensch, "Sub-10 nm carbon nanotube transistor," *Nano Lett.*, vol. 12, pp. 758–762, Jan. 2012.

- [30] A. Javey, H. Kim, M. Brink, Q. Wang, A. Ural, J. Guo, P. McIntyre, P. McEuen, M. Lundstrom, and H. Dai, "High-κ dielectrics for advanced carbon-nanotube transistors and logic gates," *Nature Mater.*, vol. 1, no. 4, pp. 241–246, Dec. 2002.

- [31] J. Deng and H.-S. P. Wong, "A compact SPICE model for carbon-nanotube field-effect transistors including nonidealities and its application-part I: Model of the intrinsic channel region," *IEEE Trans. Electron Devices*, vol. 54, no. 12, pp. 3186–3194, Dec. 2007.

- [32] N. Patil, J. Deng, S. Mitra, and H.-S. P. Wong, "Circuit-level performance benchmarking and scalability analysis of carbon nanotube transistor circuits," *IEEE Trans. Nanotechnol.*, vol. 8, no. 1, pp. 37–45, Jan. 2009.

- [33] D. Akinwande and H.-S. P. Wong, Carbon Nanotube and Graphene Device Physics. Cambridge, U.K.: Cambridge Univ. Press, 2011.

- [34] Y. Zhao, A. Liao, and E. Pop, "Multiband mobility in semiconducting carbon nanotubes," *IEEE Electron Device Lett.*, vol. 30, no. 10, pp. 1078–1080, Oct. 2009.

- [35] A. Liao, Y. Zhao, and E. Pop, "Avalanche-induced current enhancement in semiconducting carbon nanotubes," *Phys. Rev. Lett.*, vol. 101, no. 25, pp. 256804–256807, Dec. 2008.

- [36] J. Deng and H.-S. P. Wong, "Modeling and analysis of planar-gate electrostatic capacitance of 1-D FET with multiple cylindrical conducting channels," *IEEE Trans. Electron Devices*, vol. 54, no. 9, pp. 2377–2385, Sep. 2007.

- [37] M. P. Anantram and F. Léonard, "Physics of carbon nanotube devices," Rep. Progr. Phys., vol. 69, pp. 507–561, Mar. 2006.

- [38] P. M. Solomon, "Contact resistance to a one-dimensional quasi-ballistic nanotube/wire," *IEEE Electron Device Lett.*, vol. 32, no. 3, pp. 246–248, Mar. 2011.

- [39] L. Wei, D. Frank, L. Chang, and H.-S. P. Wong, "Noniterative compact modeling for intrinsic carbon-nanotube FETs: Quantum capacitance and ballistic transport," *IEEE Trans. Electron Devices*, vol. 58, no. 8, pp. 2456–2465, Aug. 2011.

- [40] Maxwell 3D, Ansoft Corp., Pittsburgh, PA, USA, 2001.

- [41] S.-H. Oh, D. Monroe, and J. M. Hergenrother, "Analytic description of short-channel effects in fully-depleted double-gate and cylindrical, surrounding-gate MOSFETs," *IEEE Electron Device Lett.*, vol. 21, no. 9, pp. 445–447, Sep. 2000.

- [42] D. Akinwande, Y. Nishi, and H.-S. P. Wong, "Analytical model of carbon nanotube electrostatics: Density of states, effective mass, carrier density, and quantum capacitance," in *Proc. IEEE Int. Electron Devices Meeting*, Dec. 2007, pp. 753–756.

- [43] F. Léonard and J. Tersoff, "Novel length scales in nanotube devices," Phys. Rev. Lett., vol. 83, no. 24, pp. 5174–5177, Dec. 1999.

- [44] S. Datta, "Conductance from transmission," in *Electronic Transport in Mesoscopic Systems*. Cambridge, U.K.: Cambridge Univ. Press, 1995, pp. 86–104.

- [45] D. Miller, Quantum Mechanics for Scientists and Engineers. New York, NY, USA: Cambridge Univ. Press, 2008.

- [46] D. Jena, T. Fang, Q. Zhang, and H. Xing, "Zener tunneling in semiconducting nanotube and graphene nanoribbon p-n junctions," Appl. Phys. Lett., vol. 93, pp. 112106–112108, Sep. 2008.

- [47] S. O. Koswatta, M. S. Lundstrom, and D. E. Nikonov, "Band-to-band tunneling in a carbon nanotube metal-oxide-semiconductor field-effect transistor is dominated by phonon-assisted tunneling," *Nano Lett.*, vol. 7, no. 5, pp. 1160–1164, Mar. 2007.

- [48] D. Akinwande, Y. Nishi, and H.-S. Wong, "Analytical derivation of the density of states, effective mass, and carrier density for achiral carbon nanotubes," *IEEE Trans. Electron Devices*, vol. 55, no. 1, pp. 289–297, Jan. 2008

- [49] Sentaurus TCAD Tools. Synopsys, Mountain View, CA, USA, 2009.

- [50] W. Haensch, Private communication, May 2012.

- [51] ITRS Roadmap. (2011) [Online]. Available: http://www.itrs.net/Links/2011ITRS/Home2011.htm

- [52] Y. Chai, A. Hazeghi, K. Takei, H.-Y. Chen, S. Yu, P. C. H. Chan, A. Javey, and H.-S. P. Wong, "Low-resistance electrical contact to carbon nanotubes with graphitic interfacial layer," *IEEE Trans. Electron Devices*, vol. 59, no. 1, pp. 12–19, Jan. 2012.

- [53] A. Javey, R. Tu, D. B. Farmer, J. Guo, R. G. Gordon, and H. Dai, "High performance *n*-type carbon nanotube field-effect transistors with chemically doped contacts," *Nano Lett.*, vol. 5, no. 2, pp. 345–348, Jan. 2005.

- [54] K. L. Grosse, M.-H. Bae, F. Lian, E. Pop, and W. P. King, "Nanoscale Joule heating, Peltier cooling and current crowding at graphene-metal contacts," *Nature Nanotechnol.*, vol. 6, no. 5, pp. 287–290, May 2011.

- [55] A. W. Cummings and F. Léonard, "Enhanced performance of short-channel carbon nanotube field-effect transistors due to gate-modulated electrical contacts," ACS Nano, vol. 6, no. 5, pp. 4494–4499, Apr. 2012.

- [56] R. H. Dennard, F. H. Gaensslen, H. N. Yu, V. L. Rideout, E. Bassous, and A. R. LeBlanc, "Design of ion-implanted MOSFET's with very small physical dimensions," *IEEE J. Solid-State Circuits*, vol. 9, no. 5, pp. 256–268, Oct. 1974.

**Jieying Luo** (S'11) received the B.S. and M.S. degrees from the Department of Physics, Peking University, Beijing, China, and Department of Electrical Engineering, Stanford University, Stanford, CA, USA, where she is currently pursuing the Ph.D. degree.

Lan Wei (S'06-M'11) received the Ph.D. degree in electrical engineering from Stanford University, Stanford, CA, USA, in 2010.

She is a Technical Staff Member with the Altera Corporation, San Jose, CA, USA.

Chi-Shuen Lee is currently pursuing the Ph.D. degree in electrical engineering with Stanford University, Stanford, CA, USA.

His research focuses on modeling and simulation of nanoelectronic and carbon nanotube devices and analysis of circuit-level performance.

**Aaron D. Franklin** (M'09) received the Ph.D. degree in electrical engineering from Purdue University, West Lafayette, IN, USA, in 2008.

His research focuses on integration of carbon-based nanomaterials into electronic devices, including high-performance transistors, thin-film transistors, supercapacitors, and photovoltaic cells.

**Ximeng Guan** (S'06–M'11) was a Post-Doctoral Scholar with the Department of Electrical Engineering, Stanford University, Stanford, CA, USA.

He is currently with the IBM Semiconductor Research and Development Center, Hopewell Junction, NY, USA, working on logic performance benchmarking.

Eric Pop (M'99–SM'11) received the Ph.D. degree from Stanford, University, Stanford, CA, USA, in 2005.

He is an Associate Professor of electrical and computer engineering with the University of Illinois Urbana-Champaign, Urbana, IL, USA.

**Dimitri A. Antoniadis** (M'79–SM'83–F'90) is the Ray and Maria Stata Professor of electrical engineering at the Massachusetts Institute of Technology, Cambridge, MA, USA.

His current research interests include nanoscale electronic devices in Si, Ge, and III-V materials.

**H.-S. Philip Wong** (S'81–M'82–SM'95–F'01) received the Ph.D. degree from Lehigh University, Bethlehem, PA, USA.

He is the Willard R. and Inez Kerr Bell Professor with the School of Engineering, Stanford University, Stanford, CA, USA.