# Capping Layers to Improve the Electrical Stress Stability of MoS<sub>2</sub> Transistors

James L. Doherty, Steven G. Noyce, Zhihui Cheng, Hattan Abuzaid, and Aaron D. Franklin\*

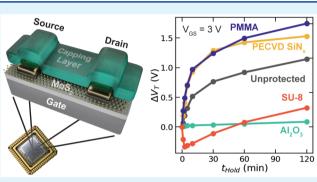

**ABSTRACT:** Two-dimensional (2D) materials offer exciting possibilities for numerous applications, including next-generation sensors and field-effect transistors (FETs). With their atomically thin form factor, it is evident that molecular activity at the interfaces of 2D materials can shape their electronic properties. Although much attention has focused on engineering the contact and dielectric interfaces in 2D material-based transistors to boost their drive current, less is understood about how to tune these interfaces to improve the long-term stability of devices. In this work, we evaluated molybdenum disulfide ( $MoS_2$ ) transistors under continuous electrical stress for periods lasting up to several days. During stress in ambient air, we observed temporary threshold

voltage shifts that increased at higher gate voltages or longer stress durations, correlating to changes in interface trap states ( $\Delta N_{it}$ ) of up to 10<sup>12</sup> cm<sup>-2</sup>. By modifying the device to include either SU-8 or Al<sub>2</sub>O<sub>3</sub> as an additional dielectric capping layer on top of the MoS<sub>2</sub> channel, we were able to effectively reduce or even eliminate this unstable behavior. However, we found this encapsulating material must be selected carefully, as certain choices actually amplified instability or compromised device yield, as was the case for Al<sub>2</sub>O<sub>3</sub>, which reduced yield by 20% versus all other capping layers. Further refining these strategies to preserve stability in 2D devices will be crucial for their continued integration into future technologies.

KEYWORDS: 2D materials, molybdenum disulfide, field-effect transistor, electrical stress, threshold voltage, passivation

## INTRODUCTION

Downloaded via DUKE UNIV on September 28, 2020 at 15:15:23 (UTC). See https://pubs.acs.org/sharingguidelines for options on how to legitimately share published articles.

Transition metal dichalcogenides (TMDs) are a class of atomically thin two-dimensional (2D) nanomaterials with many promising applications in electronics.<sup>1,2</sup> In particular, molybdenum disulfide  $(MoS_2)$  is a naturally abundant TMD with a large bandgap, making it a prime candidate for the channel material in future low-power field-effect transistors (FETs).<sup>3-6</sup> Scaled MoS<sub>2</sub> FETs commonly demonstrate impressive on-off current ratios and subthreshold swing, but obtaining consistently high drive current remains challenging.<sup>7-9</sup> Õne key issue is the highly variable room-temperature field-effect mobility commonly observed in scaled MoS<sub>2</sub> FETs.<sup>10,11</sup> While some variation could arise from imperfections in mobility extraction techniques, it is possible that much of this variation is due to disorder or charged impurities around the MoS<sub>2</sub> channel. Many methods have been investigated to reduce disorder, such as modification of the substrate chemistry underneath the channel,<sup>12-14</sup> full encapsulation of the channel with a high-k dielectric or 2D insulator such as hexagonal boron nitride,<sup>15–18</sup> and repair of sulfur vacancy defects in the  $MoS_2$  lattice.<sup>19,20</sup> Recent  $MoS_2$  FETs built on corrugated substrates even exceeded many projected mobility limits at room temperature,<sup>21</sup> indicating that the dielectric interfaces to MoS<sub>2</sub> can be engineered to resolve and even

reverse the mobility degradation issue. Further improvements at the dielectric interface will be crucial to the continued development of scaled MoS<sub>2</sub> transistors.

In addition to scaled transistors, larger form-factor  $MoS_2$  FETs have been explored for their application in photovoltaic cells,<sup>22,23</sup> nonvolatile memories,<sup>24,25</sup> and gas sensors.<sup>26–28</sup> Although resolving mobility variability is important for devices used in these applications, it is also critical for these devices to function without significant degradation over long operating lifetimes. Therefore, it is important for the structure of these devices to be designed with stability in mind. Many  $MoS_2$  FETs studied use a simple back-gated design so that the surface of the  $MoS_2$  channel is exposed. It has been shown previously that these devices are susceptible to the adsorption of oxygen and water molecules,<sup>29,30</sup> which contribute to interface trap density<sup>31</sup> and cause increased hysteresis.<sup>32–35</sup>

Received:

May 11, 2020

Accepted:

July 13, 2020

Published:

July 27, 2020

extended periods of time, the gradual accumulation or depletion of charge in these interface trap states causes the device threshold voltage  $(V_{\rm T})$  to temporarily shift.<sup>36,37</sup> These transient effects are highly undesirable, and to mitigate them it is necessary to identify effective strategies for preventing molecular adsorption onto the surface of MoS<sub>2</sub>.

One strategy for mitigating the impact of ambient exposure is the encapsulation of the MoS2 with additional layers of protection on top of the channel. Although there have been many studies to date investigating a wide variety of capping layers on MoS<sub>2</sub> FETs, their effectiveness at preventing molecular adsorption has received comparatively little attention as most have focused on how modification of the MoS2-dielectric interface can boost field-effect mobility.<sup>10,13,15–17</sup> Studies of polymer capping layers to protect MoS<sub>2</sub> FETs from the ambient have focused on fluorinated CYTOP<sup>38</sup> and p(V4D4-co-CHMA) copolymers,<sup>39</sup> although neither one appeared to completely stabilize the threshold voltage under extended periods of bias stress. One group has also studied the effects of bias stress on MoS<sub>2</sub> FETs encapsulated by hexagonal boron nitride  $(h-BN)^{40}$  and ALD-grown alumina  $(Al_2O_3)$ .<sup>41</sup> Both of these approaches significantly suppressed hysteresis in the devices, although both still allowed  $V_{\rm T}$  shifts under certain conditions. Finally, a more recent study incorporated a 3 nm-thick TiO<sub>2</sub> interfacial encapsulation layer in order to study electrical stress and the role of Fermi-level pinning at the contacts.<sup>42</sup> However, note that none of these reports have systematically examined more than one capping material for the comparative impact of electrical stress on device stability. Unfortunately, due to variations in device fabrication and characterization methodologies across the various studies, it is challenging to compare the results and identify the definitive strengths and weaknesses of diverse passivation approaches. A study of multiple passivation materials using consistent characterization techniques would reveal which passivation material properties impact the physical mechanisms that drive molecular adsorption and would guide efforts across applications with different material integration requirements.

Here, we investigated the effects of gate- and drain-bias stress on MoS<sub>2</sub> field-effect transistors capped with a variety of passivation layers, including a study of the impact of the electrical stress on device operation under ambient air conditions. We further explored the sensitivity of the devices to variations in stress time and voltage. After baseline device characterization, MoS<sub>2</sub> channels were covered with a variety of capping layers, including poly(methyl methacrylate) (PMMA), SU-8 photoresist, silicon nitride  $(SiN_x)$ , and aluminum oxide  $(Al_2O_3)$ . The hydrophilic PMMA layer proved to be ineffective passivation, while the much thicker and hydrophobic SU-8 film provided notable improvements, particularly in short-term stress tests. Devices capped with SiN<sub>x</sub> were surprisingly unstable, likely due to defects introduced during film deposition. Only the Al<sub>2</sub>O<sub>3</sub>-passivated devices demonstrated full stability with no discernible threshold voltage shift after days of continuous bias; yet, the atomic layer deposition (ALD) process for the  $Al_2O_3$  also resulted in the lowest device yield compared to the other passivation layers. These results shed light on the role of interface control and passivation material selection in the electrical stability and yield of MoS<sub>2</sub>based devices, highlighting some key trade-offs.

## RESULTS AND DISCUSSION

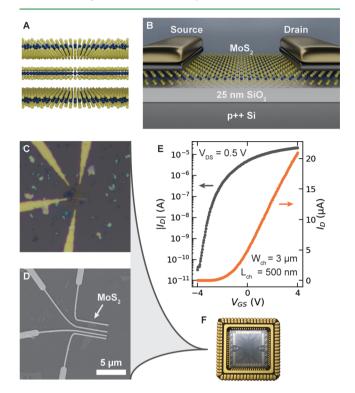

The  $MoS_2$  FETs were fabricated using conventional lithography and thin-film deposition techniques.  $MoS_2$  flakes (whose molecular diagram is shown in Figure 1A) were mechanically

**Figure 1.**  $MoS_2$  FET device structure and wire-bonding for long-term characterization. (A) Molecular diagram of the van der Waals-layered structure of  $MoS_2$ . (B) Device schematic of a back-gated  $MoS_2$  FET with 10 nm Ni (topped with 20 nm Pd) source/drain contacts. (C) Optical microscope and (D) SEM image of a set of three devices with different channel lengths. (E) Typical transfer and subthreshold characteristics of a device measured in ambient conditions. (F) Chip installed and wire-bonded into chip carrier for testing at the end of fabrication.

exfoliated from a bulk crystal (2D Semiconductors Inc.) onto highly doped p++ silicon wafers with a 25 nm thick thermal oxide. Thin multilayer MoS<sub>2</sub> flakes (approximately 4-8 nm thick, see Figure S1 in the Supporting Information) were identified by an optical contrast technique developed previously,<sup>43,44</sup> after which metal contacts were defined by electron-beam lithography, electron-beam evaporation, and metal lift-off. A schematic of the finished device is shown in Figure 1B with optical and SEM images of typical devices shown in Figure 1C,D. Electrical characterization (Figure 1E) was performed using Keysight B2900A source measure units under ambient conditions unless otherwise specified. To facilitate extensive long-term testing, many completed chips were wire-bonded to ceramic packages (Figure 1F) that fit the sockets on custom measurement systems, as previously described.45 A full description of fabrication and characterization procedures is available in the Supporting Information along with a detailed extraction of performance metrics for all devices studied (see Table S1, Figures S2-S8). Of particular note in Table S1 are the "initial device yield" percentages recorded for every chip, showing that yield improved from  $\sim$ 30% up to  $\sim$ 81% by several simple fabrication improvements including using sufficiently wide metal lines for signal routing,

**Figure 2.** Susceptibility of nonpassivated MoS<sub>2</sub> FETs to molecular adsorption from ambient air conditions. (A) Long-term biasing of a MoS<sub>2</sub> FET in ambient air at  $V_{\text{DS}} = 0.5$  V and  $V_{\text{GS}} = 3$  V with periodic interruptions every 2 h to measure transfer characteristics ( $V_{\text{GS}}$  sweep). (B) Transfer curves measured throughout the experiment in (A), showing a positive threshold voltage shift as a result of the accumulation of adsorbed species on the surface of the MoS<sub>2</sub> channel. (C) Transfer curves measured after 2 h of biasing at a static gate voltage; tested for  $V_{\text{GS}} = -4$  V to +4 V in increments of 1 V. (D) Magnitude of threshold voltage shifts extracted from (C), showing equal and opposite shifts for positive and negative  $V_{\text{GS}}$  bias voltages, where the dual axis shows the corresponding estimated change in interface trap occupancy. (E) Transfer curves measured after biasing at a static gate voltage shifts and change in interface trap occupancy. (E), showing their fit to a stretched exponential bias-stress model.  $L_{ch} = 500$  nm and  $W_{ch} = 3 \mu m$  for this device.

avoiding very thick  $MoS_2$  flake deposits, and limiting electrical connection between devices so that individual failures are isolated. The total yield of  $MoS_2$  devices in this study finished at 49% (100 out of 204 devices).

Prior to studying the influence of different capping layers on MoS<sub>2</sub> FET stability and performance, baseline back-gated devices were fully characterized. Because of previous reports  $^{36,37}$  of the threshold voltage instability of  $MoS_2$ transistors under bias stress, focus was given to this behavior in our devices. Figure 2A shows the results of an experiment in which a MoS<sub>2</sub> FET was held in the on-state with a drain voltage of  $V_{\text{DS}}$  = 0.5 V and a gate voltage of  $V_{\text{GS}}$  = 3 V for four consecutive time segments of length  $t_{\text{Hold}} = 2$  h. Between biasstress segments, the gate voltage was swept in order to extract the device characteristics shown in Figure 2B. From the initial device behavior, there is a positive threshold voltage shift  $(\Delta V_{\rm T})$  in each of the other four measurements of the transfer characteristics. This simple experiment yields several important insights into the back-gated, nonpassivated MoS<sub>2</sub> FET operating in ambient air: (1) even though we applied constant drain and gate voltages, the drain current was not constant over time, changing by up to 45% from its initial value; (2) the drain current was changing because the threshold voltage of the device was changing; (3) the act of sweeping the gate voltage partially reset the threshold voltage shift in the device, but in the subsequent period of t<sub>Hold</sub> the threshold voltage returned to the same terminal value; and (4) this process is repeatable, indicating that most of these effects are transient

rather than permanent changes to the device. This unstable behavior was extremely consistent across many devices on different chips and wafers, including those with significantly different oxide thicknesses (see Figures S9–S11 for identical behavior in multilayer and monolayer devices on 90 nm SiO<sub>2</sub> substrates). In particular, the consistent behavior of the monolayer device (Figure S11) suggests that the stability issues observed in this work are dominated by extrinsic interfacial or dielectric-layer traps, since there is little apparent dependence on MoS<sub>2</sub> thickness.

Repeating the experiment shown in Figure 2A under low vacuum or in dry nitrogen conditions (see Figure S12) yielded a significant improvement in threshold voltage stability, consistent with previous reports.<sup>37</sup> This indicates that the dominant factor driving this behavior is the adsorption and desorption of oxygen and water molecules from the ambient air onto the surface of the MoS2 channel. The impact of applying different polarity and magnitude of gate voltage to the device is seen in Figure 2C with the magnitudes of  $\Delta V_{\rm T}$ resulting from each bias stress  $V_{GS}$  shown in Figure 2D. There is a clear linear dependence of  $\Delta V_{\rm T}$  on the stress gate voltage that is symmetric for positive and negative gate voltages. This symmetry demonstrates that traps can just as easily be filled or emptied by applying a positive or negative gate voltage; however, interestingly the subthreshold swing (SS) is not symmetric, improving under negative stress and slightly degrading under positive stress (see Figure S13). Since SS degradation is associated with increased trap states, this

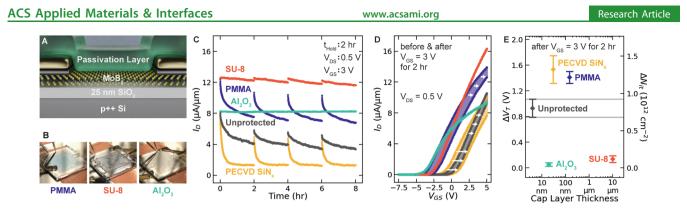

**Figure 3.** Accumulation of trapped charge with different passivation layers capping back-gated  $MoS_2$  FETs when stressed for 2 h intervals. (A) Modified device schematic with passivation layer. (B) Photographs of chips coated in a variety of passivation layers. (C) Long-term biasing of  $MoS_2$  FETs with different passivation layers, performed in ambient conditions with periodic interruptions every 2 h to measure transfer characteristics. (D) Transfer curves measured before and after the first 2 h of biasing shown in (C). (E) Magnitude of threshold voltage shift and corresponding approximate change in interface trap occupancy at the end of 2 h of biasing at  $V_{DS} = 0.5$  V and  $V_{GS} = 3$  V. Error bars show the mean and standard deviation of measurements from three different devices on each chip.  $L_{ch} = 500$  nm for all devices shown.

suggests that positive stress is filling electron traps while negative stress is emptying those traps. The symmetry in  $\Delta V_{\rm T}$  is consistent with other reports of the nonpassivated MoS<sub>2</sub> FET,<sup>37</sup> but note that this behavior is not always symmetrical, as seen in CYTOP-passivated MoS<sub>2</sub> FETs which show larger  $\Delta V_{\rm T}$  under negative gate voltage stress.<sup>38</sup>

Although the observed  $\Delta V_{\rm T}$  is indicative of the behavior of trapped charges in these devices,  $V_{\rm T}$  itself can vary widely across the device structures reported in different studies so it is preferable to use a different metric, such as change in interface trap occupancy  $(\Delta N_{it})$ , that does not depend on the gate oxide thickness. By assuming a parallel plate capacitor model<sup>15</sup> for the oxide capacitance of the 2D FET structure, we are able to directly convert  $\Delta V_{\rm T}$  to the change in surface charge on the MoS<sub>2</sub> flake. A change in the surface charge during bias stress indicates that there has been a change in the density of electrons or holes occupying trap states  $(N_{it})$  at the gate oxide interface. Therefore, we are able to use the inset equation in Figure 2D to compute an approximated change in  $N_{\rm it}$  that corresponds to the observed  $\Delta V_{\rm T}$ , which is shown on the secondary axis of Figure 2D. The usefulness of  $\Delta N_{it}$  as a figure of merit is highlighted more in the Supporting Information, which shows a device fabricated on a different substrate (90 nm SiO<sub>2</sub>) experiencing the same stress as Figure 2C,D and exhibiting an almost identical relationship between gate bias and  $\Delta N_{it}$  (see Figure S10). As a final note, for a sheet of charge with density  $10^{12}$  cm<sup>-2</sup>, the nearest-neighbor spacing was calculated to be approximately 10 nm, which was found to be a helpful metric for visualizing  $N_{it}$  (see Figure S14).

The final aspect of the baseline  $MoS_2$  FETs that was investigated is the impact of stress time at a constant gate stress voltage, as shown in Figure 2E,F. Here we see that  $V_T$  evolves over time according to the same stretched-exponential model that has been widely used to model bias stress in  $MoS_2$ transistors<sup>39,46</sup> as well as thin-film transistors based on zinc oxides<sup>47,48</sup> or organic semiconductors<sup>49,50</sup>

$$\Delta V_{\rm T}(t) = V_0 \left( 1 - \exp\left[ -\left(\frac{t}{\tau}\right)^{\beta} \right] \right)$$

where  $V_0$  is the value of  $\Delta V_T$  as  $t \to \infty$  and  $\tau$  is known as the relaxation time. The solid line in Figure 2F shows a fit to the experimental data with  $\beta$  of 0.65 and a relaxation time of 4500 s (1.25 h). Hence, the time scale over which these FETs should

be analyzed for electrical stress behavior should be on the order of 1-2 h.

To briefly summarize, the baseline, back-gated  $MoS_2$  FETs experienced a threshold voltage shift under gate bias stress largely driven by  $O_2$  and  $H_2O$  molecules in the ambient air environment. This threshold voltage instability exhibited a linear dependence on the stress voltage and a stretched-exponential dependence on stress time with the majority of the change occurring within the first 2 h of stress but with several hundred millivolts of shift happening within the first few minutes. For many applications of  $MoS_2$  FETs, this bias-induced drifting behavior of the threshold voltage would be unacceptable.

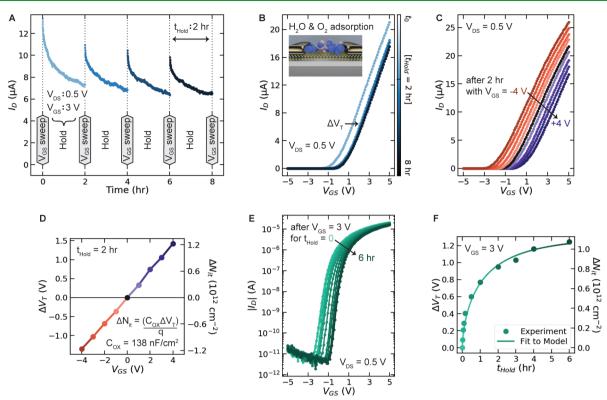

To passivate  $MoS_2$  transistors in an effort to eliminate these deleterious effects of bias stress, we explored the incorporation of four distinct protective barrier layers to cover the exposed  $MoS_2$  channel. Figure 3A illustrates the modified device schematic with the introduction of a passivation layer, and Figure 3B shows several of the actual chips with the central device area covered with a passivation layer. The results of the bias stress test at a fixed  $V_{GS} = 3$  V (as presented for the baseline, nonpassivated device in Figure 2A,B) reveal that some of the passivation layers actually exacerbate the threshold voltage shifts while others ameliorate them (Figure 3C,D). To improve statistical rigor, the experiments shown in Figure 3C,D were repeated on three separate devices on each chip with the final results (mean and standard deviation) summarized in Figure 3E.

Selection of the four capping layers was made to explore distinct deposition and material differences. PMMA was spincoated and is commonly used as a passivation coating for research-level devices. SU-8 was also spin-coated but is significantly thicker than PMMA and is known for its effective resistance to permeation, including in liquid environments.<sup>51–53</sup> The  $SiN_x$  was deposited by plasma-enhanced chemical vapor deposition (PECVD), which introduces potential damage to the MoS<sub>2</sub> during deposition but is also a more standard passivation material for solid-state devices. Finally, Al<sub>2</sub>O<sub>3</sub> was grown via atomic layer deposition (ALD), which is a less aggressive reactive environment (compared to PECVD) and allows for precise and comparatively thin film deposition (20 nm in this case). This variety of passivation films allows for insight into which offers the most effective protection of MoS<sub>2</sub> from ambient effects while preserving the

www.acsami.org

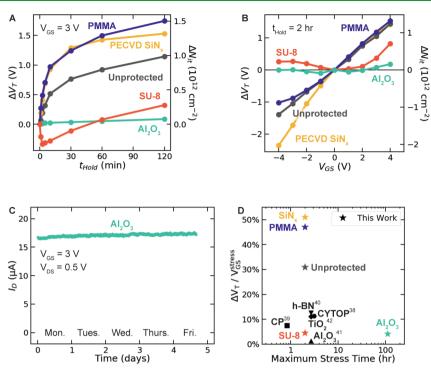

Figure 4. Reduction of trapped charge accumulation by the addition of passivation layers to back-gated MoS<sub>2</sub> FETs and the impact of bias stress time and voltage. (A) Comparison of interface trap accumulation under a variety of passivation layers as a function of bias time and (B) as a function of gate bias voltage. (C) Long-term biasing of MoS<sub>2</sub> FET passivated with  $Al_2O_3$  showing stability over several days. Measurements were captured continuously and saved every 10 s for the entire duration. (D) Benchmarking  $V_T$  shift versus maximum stress time against other encapsulation demonstrations for MoS<sub>2</sub> FETs. Percent  $V_T$  shift was obtained by normalizing absolute  $V_T$  shift by the magnitude of  $V_{GS}$  applied during stress. Note that exact device structure and stress conditions vary, but all values are taken for positive  $V_{GS}$  stress.

intrinsic  $MoS_2$  electrical properties. Detailed analysis of each capping layer is available in the Supporting Information, including the subthreshold curves for all 76 devices fabricated (Figures S3–S8) and the extraction of any aggregate changes in transconductance, threshold voltage, or subthreshold swing that occurred as a result of encapsulation.

One first point of interest in Figure 3C,D is the relative device current levels at  $V_{GS}$  = 3 V. In general, the polymercapped devices (PMMA and SU-8) displayed slightly higher width-normalized on-current due to a combination of their negative threshold voltage and their ability to sustain high transconductance across a wide voltage range. In contrast, the Al<sub>2</sub>O<sub>3</sub>-capped device in Figure 3D shows a similar threshold voltage but a more substantial roll-off in transconductance in the on-state, leading to an overall lower current at  $V_{GS}$  = 3 V. It is also striking how similar in shape the PMMA-capped response over time is to the baseline unprotected device (Figure 3C), indicating that the PMMA offers no noticeable improvement in device stability. Although the SiN<sub>x</sub>-capped device begins at a similar current level to the baseline device, it falls precipitously in a short time and displays the most severe threshold voltage instability. Lastly, both the Al<sub>2</sub>O<sub>3</sub>-capped and SU-8-capped devices show improvement in stability compared to the baseline with the Al<sub>2</sub>O<sub>3</sub> device showing the flattest and most stable response over time (Figure 3C).

The PMMA-capped devices displayed such a large threshold voltage shift in Figure 3D at least in part because the introduction of PMMA caused a distinct permanent negative threshold voltage shift in all devices tested (see Figure S3). As previous reports have indicated, this is because devices susceptible to bias stress instability will tend to shift until  $V_{\rm T} = V_{\rm GS}$ .<sup>48,49</sup> Therefore, because the PMMA-capped devices had

more negative initial  $V_{\rm T}$  and they were experiencing the same  $V_{\rm GS}$  = 3 V during stress as all the other devices in Figure 3C,D, they "had further to go" in a sense and thus experienced a  $V_{\rm T}$ shift that was larger than the baseline unprotected device. Note that if the PMMA had been an effective passivation layer, then we would not have expected to see any threshold voltage shift in Figure 3D, regardless of how negative  $V_{\rm T}$  was to begin with. Exactly why PMMA was unable to prevent molecular adsorption onto the surface of MoS<sub>2</sub> remains unclear, but some researchers have proposed that PMMA films can form pockets of air on the surface of 2D materials,<sup>54</sup> leading to oxidation and degradation of sensitive 2D materials over extended periods of time. This bias-stress performance of PMMA is most comparable to results from p(V4D4-co-CHMA) copolymer,<sup>39</sup> which yielded devices that were only slightly more stable than PMMA and with roughly similar threshold voltage and transconductance. Regardless, it is clear that the PMMA provided inadequate protection.

The SiN<sub>x</sub>-capped devices also experienced larger  $V_{\rm T}$  shifts under stress, even though their threshold voltages were much closer to the uncapped device (see Figure S5). However, it is important to note that the SiN<sub>x</sub> capping layer was deposited by PECVD, during which the MoS<sub>2</sub> was exposed to a 50 W silane plasma for at least the first few seconds of deposition. We expect that this process damaged the MoS<sub>2</sub> crystal structure, and it is possible that having a higher density of surface defects could enhance molecular adsorption during bias stress, as has been previously suggested for oxygen adsorption in particular.<sup>55,56</sup> Enhanced trap filling could account for the higher  $V_{\rm T}$ shifts and the three times steeper drain current settling for SiN<sub>x</sub> seen in Figure 3C (see also Figure S15 for comparison of settling time constants). The thickness of 30 nm for our SiN<sub>x</sub>

encapsulation was chosen based on another report of encapsulated  $MoS_2$  FETs,<sup>32</sup> but based on these results and more extensive review<sup>57</sup> it now seems most likely that our PECVD tool is incapable of producing such a thin film without any pinhole defects that allow molecular adsorbents to reach the  $MoS_2$  surface.

The results of initial tests in Figure 3 examining  $V_{\rm T}$  shift after 2 h bias-stress intervals were promising for devices capped by either SU-8 photoresist or ALD-grown Al<sub>2</sub>O<sub>3</sub>. A more rigorous methodology of exploring stress time and voltage was carried out (Figure 4A,B) to examine further differences between the various passivation materials. From the results of Figure 4A, it was discovered that devices capped by SU-8 experienced an initial threshold voltage shift in the opposite direction that was masking an underlying, long-term trend in  $V_{\rm T}$  that is similar to the unmodified devices; that is, the SU-8-capped devices first exhibited an abrupt negative  $V_{\rm T}$  shift over the initial minutes of bias stress, followed by a more gradual positive shift that resulted in a net change after 2 h that was actually rather small (hence, the results of Figure 3C). From Figure 4B, we further see that SU-8 does not follow the linear trend of  $V_{\rm T}$  shifting under increasingly positive gate-stress bias seen in all other devices and shows a net positive  $V_{\rm T}$  shift after 2 h of bias at any voltage. Both of these distinctions in bias stress behavior for the SU-8-passivated devices are attributed to the existence of new and different trap states at the MoS<sub>2</sub>-polymer interface. Because the threshold voltage shift is always net positive after 2 h, this means the trap states are filling with net negative charge. This could indicate a different mechanism is taking place, such as the injection of negatively charged hot carriers into the dielectric over the extended duration of bias. Importantly, the behavior observed in Figure 4A for the SU-8-capped device was reversible as the trend was reproduced on the same device.

Despite the unique threshold voltage shifting behavior exhibited by the SU-8-passivated devices, qualitatively they performed quite well and certainly far better than the completely unprotected, PMMA-passivated or SiN<sub>x</sub>-passivated devices. Additionally, the spin-coating encapsulation process was facile and had high yield ( $\sim$ 90%), especially compared to the reduced yield observed for devices with ALD Al<sub>2</sub>O<sub>3</sub> passivation layers ( $\sim$ 70%). These yield percentages are listed in Table S1 as the "post-capping yield" and were calculated from the number of functioning devices that survived the encapsulation step; hence, this provides an indication of how "risky" each process is for the devices. Devices were determined to fail to survive encapsulation if (1) their oncurrent reduced to effectively zero or, more commonly, (2) their gate current increased to more than 50 nA. Interestingly, while PECVD SiN, devices did not perform well, that process had actually very high yield as well (90%), possibly because it was so fast and the devices only spent a couple of minutes in the chamber at elevated temperature (unlike ALD, which takes several hours at 120 °C). The reason this metric is critical for comparing capping layers is that many applications can become prohibitively expensive if yield is compromised too early in the fabrication processes. Importantly, SU-8 stands alone as the only capping layer that substantially improves device stability while also maintaining high yield. Finally, the SU-8 device instabilities were not obvious in Figure 3 and only actually uncovered by the rigorous tests shown in Figure 4; the overall passivation quality is clearly good enough for there to be several reports of SU-8 encapsulation improving the shelf life of air-sensitive thin-film transistors.<sup>58,59</sup> For these reasons,

we are optimistic that SU-8 can still be a good choice for most applications.

Another important takeaway from the gate bias-dependent threshold voltage shift data shown in Figure 4B is how consistent the response of the PMMA-passivated and SiN<sub>x</sub>passivated devices are with the unprotected device. This is evidence that the trap mechanisms responsible for  $V_{\rm T}$ instability in the unprotected device remain largely unaffected by these capping layers. While we cannot rule out the introduction of additional traps within the PMMA or SiN<sub>r</sub> capping layers, we would not have expected the curves in Figure 4B to match so well if that were the case. The reality may be a combination of both internal traps within the PMMA and SiN<sub>x</sub> with molecular adsorption via diffusion still playing a key role through PMMA air pockets or SiN<sub>x</sub> pinholes. In contrast, the SU-8 and Al<sub>2</sub>O<sub>3</sub> both offer appreciable improvements to the  $V_{\rm T}$  shifting behavior under the varying gate stress magnitude and polarity with the Al<sub>2</sub>O<sub>3</sub> offering slightly better protection than the spin-coated polymer. This overall consistency in behavior (PMMA consistent with  $SiN_x$  and also SU-8 consistent with  $Al_2O_3$ ) seen across capping layers that have otherwise such different physical properties (in addition to the evidence from Figure S12 for molecular adsorption as a dominant mechanism) inspires confidence that these results should be more broadly applicable to other 2D material systems in addition to MoS<sub>2</sub>. Notably, alumina passivation on black phosphorus (BP) FETs has already been shown to both protect from ambient degradation and to enhance electrical stress stability.<sup>60,61</sup> In addition, tungsten selenide (WSe<sub>2</sub>) FETs have been shown to be susceptible to ptype doping from oxygen adsorption.<sup>62</sup> Compared to MoS<sub>2</sub>, however, experimental demonstrations of electrical stress in these FETs are much more sparse, and therefore we believe additional study of the specific effect of passivation on stress stability is warranted.

Ultimately, the Al<sub>2</sub>O<sub>3</sub>-capped devices exhibited the most encouraging stability under all bias stress conditions, demonstrating negligible changes in  $V_{\rm T}$  even after days of continuous bias stress, as shown in Figure 4C. However, as previously noted, it is significant that Al<sub>2</sub>O<sub>3</sub> devices showed the lowest post-capping yield, and so this is worth a closer look. A key problem was that any devices capped with  $Al_2O_3$ experienced a substantial negative threshold voltage shift immediately after deposition of the film, making it often impossible to gate the device fully off (see Figure S16). This effect is commonly observed in Al<sub>2</sub>O<sub>3</sub>-capped devices,<sup>63</sup> and it indicates that the ALD films contain a significant amount of built-in fixed positive charge (such as unsatisfied Al<sup>+</sup> dangling bonds). We found this effect to be most prominent for 40 and 30 nm thick  $Al_2O_3$  films, which is why the devices reported herein were only coated with 20 nm of  $Al_2O_3$ . More details can be found in the Supporting Information, and while these effects could potentially be overcome by further process optimization, at present the hampered yield of Al<sub>2</sub>O<sub>3</sub>-capped devices is a nontrivial cost to its use as a passivation layer. All of this is in contrast to the SU-8-capped devices, which demonstrated close to ideal yield for all devices tested and displayed the next-best electrical stability. Since SU-8 has also further shown compatibility as a passivation layer in biosensors and other liquid environments, it could therefore prove valuable for MoS<sub>2</sub> FETs used in this capacity.<sup>51–53</sup>

A benchmarking comparison of the threshold voltage shift versus bias stress time is provided in Figure 4D. While this

comparison looks only at one aspect of the electrical stability, it does reveal that both the SU-8 and Al<sub>2</sub>O<sub>3</sub> provide stability that is on par with the best previously reported approaches and for longer bias stress durations. The overall performance of the  $Al_2O_3$ -capped devices is consistent with the one other report<sup>41</sup> of bias stress in an MoS<sub>2</sub> FET. It is notable that Illarionov et al.<sup>41</sup> report pushing their devices to a gate stress field of 4.8 MV/cm, while we were limited to 1.6 MV/cm by some of the large metal features required for wire-bonding our devices (these chip features are even visible to the naked eye in Figure 1F). With metal features of this size, our backside gate oxide was far more susceptible to breakdown if we exceeded a field of 2 MV/cm for hours at a time. While they report higher stress fields, we report more than an order of magnitude longer stress duration, which is an equally important metric, particularly for applications that do not require high voltage. Since we have seen here that stress intensity and duration both contribute to the device response, it is reassuring that our two different approaches produced similar results.

## CONCLUSION

In conclusion, we have investigated the bias stress stability of MoS<sub>2</sub> field-effect transistors in ambient air under a variety of stress times and voltage conditions. In uncapped devices, we observed substantial threshold voltage shifts occurring primarily in the first 2 h of stress with the magnitude and polarity of the shift depending linearly on the gate voltage under stress. These effects correlated to changes in interface charge trap density of up to  $10^{12}$  cm<sup>-2</sup> but were fully reversible and significantly reduced under vacuum or dry nitrogen conditions, leading us to explore several capping layers to protect the devices. Devices capped with PMMA and PECVD SiN<sub>x</sub> showed no improvement or even worse electrical stability, while an SU-8 capping layer provided some notable improvement with a facile deposition process and very high device yield. ALD Al2O3-capped devices demonstrated the best stability with no observable change in threshold voltage even after 5 days of continuous stress but also showed low device yield after passivation. These results demonstrate the importance of developing a rigorous characterization methodology when evaluating the stability of devices under stress to expose the flaws of unstable devices and the appropriateness of certain passivation layers. Not every capping layer is equally effective for protecting the channel of MoS<sub>2</sub> transistors, but one can be selected with care to produce devices that operate in ambient air with no sign of instability. This shows promise for the continued development and integration of air-stable 2D transistors into future electronic devices and sensors.

## ASSOCIATED CONTENT

## **Supporting Information**

The Supporting Information is available free of charge at https://pubs.acs.org/doi/10.1021/acsami.0c08647.

Detailed description of processes used in the fabrication of the  $MoS_2$  FETs, additional electrical characterization of each chip, comparison to multilayer and monolayer devices on 90 nm-SiO<sub>2</sub> substrates, and long-term characterization tests in vacuum and dry nitrogen environments (PDF)

## AUTHOR INFORMATION

#### **Corresponding Author**

Aaron D. Franklin – Department of Electrical and Computer Engineering and Department of Chemistry, Duke University, Durham, North Carolina 27708, United States; orcid.org/ 0000-0002-1128-9327; Email: aaron.franklin@duke.edu

#### Authors

- James L. Doherty Department of Electrical and Computer Engineering, Duke University, Durham, North Carolina 27708, United States; © orcid.org/0000-0003-1571-0622

- Steven G. Noyce Department of Electrical and Computer Engineering, Duke University, Durham, North Carolina 27708, United States; © orcid.org/0000-0002-2953-7560

- Zhihui Cheng Department of Electrical and Computer Engineering, Duke University, Durham, North Carolina 27708, United States; © orcid.org/0000-0003-1285-0523

- Hattan Abuzaid Department of Electrical and Computer Engineering, Duke University, Durham, North Carolina 27708, United States; © orcid.org/0000-0002-6712-4644

Complete contact information is available at: https://pubs.acs.org/10.1021/acsami.0c08647

#### **Author Contributions**

J.L.D. and A.D.F. conceived the study. J.L.D. fabricated the devices, designed the experiments, and performed the device measurements. S.G.N. aided in the experimental design. Z.C. and H.A. contributed to device fabrication processes. A.D.F. supervised the research and provided scientific guidance. All authors contributed to the writing of the manuscript.

#### Notes

The authors declare no competing financial interest.

#### ACKNOWLEDGMENTS

This work was supported in part by NSF Grant ECCS-1915814 and NIH Grant 1R01HL146849. This work was performed in part at the Duke University Shared Materials Instrumentation Facility (SMIF), which is a member of the North Carolina Research Triangle Nanotechnology Network (RTNN), which is supported by the National Science Foundation (Grant ECCS-1542015) as part of the National Nanotechnology Coordinated Infrastructure (NNCI).

#### REFERENCES

Franklin, A. D. Nanomaterials in Transistors: From High-Performance to Thin-Film Applications. *Science* 2015, 349, aab2750.

Novoselov, K. S.; Mishchenko, A.; Carvalho, A.; Castro Neto, A. H. 2D Materials and Van der Waals Heterostructures. *Science* 2016, 353, aac9439.

(3) Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Single-layer MoS<sub>2</sub> Transistors. *Nat. Nanotechnol.* **2011**, *6*, 147–150.

(4) Desai, S. B.; Madhvapathy, S. R.; Sachid, A. B.; Llinas, J. P.; Wang, Q.; Ahn, G. H.; Pitner, G.; Kim, M. J.; Bokor, J.; Hu, C.; Wong, H.-S. P.; Javey, A.  $MoS_2$  Transistors with 1-Nanometer Gate Lengths. *Science* **2016**, *354*, 99–102.

(5) Liu, H.; Neal, A. T.; Ye, P. D. Channel Length Scaling of  $MoS_2$  MOSFETs. ACS Nano 2012, 6, 8563–8569.

(6) Su, Y.; Kshirsagar, C. U.; Robbins, M. C.; Haratipour, N.; Koester, S. J. Symmetric Complementary Logic Inverter Using Integrated Black Phosphorus and MoS<sub>2</sub> Transistors. 2D Mater. **2016**, 3, No. 011006.

(7) Das, S.; Chen, H.-Y.; Penumatcha, A. V.; Appenzeller, J. High Performance Multilayer  $MoS_2$  Transistors with Scandium Contacts. *Nano Lett.* **2013**, *13*, 100–105.

www.acsami.org

(8) Liu, Y.; Guo, J.; Wu, Y.; Zhu, E.; Weiss, N. O.; He, Q.; Wu, H.; Cheng, H. C.; Xu, Y.; Shakir, I.; Huang, Y.; Duan, X. Pushing the Performance Limit of Sub-100 nm Molybdenum Disulfide Transistors. *Nano Lett.* **2016**, *16*, 6337–6342.

(9) Cheng, Z.; Price, K.; Franklin, A. D. Contacting and Gating 2-D Nanomaterials. *IEEE Trans. Electron Devices* **2018**, *65*, 4073–4083.

(10) Cui, X.; Lee, G. H.; Kim, Y. D.; Arefe, G.; Huang, P. Y.; Lee, C. H.; Chenet, D. A.; Zhang, X.; Wang, L.; Ye, F.; Pizzocchero, F.; Jessen, B. S.; Watanabe, K.; Taniguchi, T.; Muller, D. A.; Low, T.; Kim, P.; Hone, J. Multi-Terminal Transport Measurements of MoS<sub>2</sub> Using a Van der Waals Heterostructure Device Platform. *Nat. Nanotechnol.* **2015**, *10*, 534–540.

(11) Liu, Y.; Wu, H.; Cheng, H.-C.; Yang, S.; Zhu, E.; He, Q.; Ding, M.; Li, D.; Guo, J.; Weiss, N. O.; Huang, Y.; Duan, X. Toward Barrier Free Contact to Molybdenum Disulfide Using Graphene Electrodes. *Nano Lett.* **2015**, *15*, 3030–3034.

(12) Najmaei, S.; Zou, X.; Er, D.; Li, J.; Jin, Z.; Gao, W.; Zhang, Q.; Park, S.; Ge, L.; Lei, S.; Kono, J.; Shenoy, V. B.; Yakobson, B. I.; George, A.; Ajayan, P. M.; Lou, J. Tailoring the Physical Properties of Molybdenum Disulfide Monolayers by Control of Interfacial Chemistry. *Nano Lett.* **2014**, *14*, 1354–1361.

(13) Bao, W.; Cai, X.; Kim, D.; Sridhara, K.; Fuhrer, M. S. High Mobility Ambipolar  $MoS_2$  Field-Effect Transistors: Substrate and Dielectric Effects. *Appl. Phys. Lett.* **2013**, *102*, No. 042104.

(14) Bolshakov, P.; Zhao, P.; Azcatl, A.; Hurley, P. K.; Wallace, R. M.; Young, C. D. Improvement in Top-Gate MoS<sub>2</sub> Transistor Performance Due to High Quality Backside Al<sub>2</sub>O<sub>3</sub> Layer. *Appl. Phys. Lett.* **2017**, *111*, No. 032110.

(15) Radisavljevic, B.; Kis, A. Mobility Engineering and a Metal-Insulator Transition in Monolayer MoS<sub>2</sub>. *Nat. Mater.* **2013**, *12*, 815–820.

(16) Zou, X.; Wang, J.; Chiu, C.-H.; Wu, Y.; Xiao, X.; Jiang, C.; Wu, W.-W.; Mai, L.; Chen, T.; Li, J.; Ho, J. C.; Liao, L. Interface Engineering for High-Performance Top-Gated MoS<sub>2</sub> Field-Effect Transistors. *Adv. Mater.* **2014**, *26*, 6255–6261.

(17) Li, X.; Xiong, X.; Li, T.; Li, S.; Zhang, Z.; Wu, Y. Effect of Dielectric Interface on the Performance of  $MoS_2$  Transistors. ACS Appl. Mater. Interfaces 2017, 9, 44602–44608.

(18) Lee, G. H.; Cui, X.; Kim, Y. D.; Arefe, G.; Zhang, X.; Lee, C. H.; Ye, F.; Watanabe, K.; Taniguchi, T.; Kim, P.; Hone, J. Highly Stable, Dual-Gated MoS<sub>2</sub> Transistors Encapsulated by Hexagonal Boron Nitride with Gate-Controllable Contact, Resistance, and Threshold Voltage. *ACS Nano* **2015**, *9*, 7019–7026.

(19) Yu, Z.; Pan, Y.; Shen, Y.; Wang, Z.; Ong, Z.-Y.; Xu, T.; Xin, R.; Pan, L.; Wang, B.; Sun, L.; Wang, J.; Zhang, G.; Zhang, Y. W.; Shi, Y.; Wang, X. Towards Intrinsic Charge Transport in Monolayer Molybdenum Disulfide by Defect and Interface Engineering. *Nat. Commun.* **2014**, *5*, 5290.

(20) Yu, Z.; Ong, Z.-Y.; Pan, Y.; Cui, Y.; Xin, R.; Shi, Y.; Wang, B.; Wu, Y.; Chen, T.; Zhang, Y.-W.; Zhang, G.; Wang, X. Realization of Room-Temperature Phonon-Limited Carrier Transport in Monolayer MoS<sub>2</sub> by Dielectric and Carrier Screening. *Adv. Mater.* **2016**, *28*, 547– 552.

(21) Liu, T.; Liu, S.; Tu, K. H.; Schmidt, H.; Chu, L.; Xiang, D.; Martin, J.; Eda, G.; Ross, C. A.; Garaj, S. Crested Two-Dimensional Transistors. *Nat. Nanotechnol.* **2019**, *14*, 223–226.

(22) Tsai, M. L.; Su, S. H.; Chang, J. K.; Tsai, D. S.; Chen, C. H.; Wu, C. I.; Li, L. J.; Chen, L. J.; He, J. H. Monolayer  $MoS_2$  Heterojunction Solar Cells. *ACS Nano* **2014**, *8*, 8317–8322.

(23) Pezeshki, A.; Shokouh, S. H. H.; Nazari, T.; Oh, K.; Im, S. Electric and Photovoltaic Behavior of a Few-Layer  $\alpha$ -MoTe<sub>2</sub>/MoS<sub>2</sub> Dichalcogenide Heterojunction. *Adv. Mater.* **2016**, *28*, 3216–3222.

(24) Sangwan, V. K.; Lee, H. S.; Bergeron, H.; Balla, I.; Beck, M. E.; Chen, K. S.; Hersam, M. C. Multi-Terminal Memtransistors from Polycrystalline Monolayer Molybdenum Disulfide. *Nature* **2018**, *554*, 500–504.

(25) Bertolazzi, S.; Krasnozhon, D.; Kis, A. Nonvolatile Memory Cells Based on MoS2/Graphene Heterostructures. *ACS Nano* **2013**, *7*, 3246–3252. (26) Liu, B.; Chen, L.; Liu, G.; Abbas, A. N.; Fathi, M.; Zhou, C. High-Performance Chemical Sensing Using Schottky-Contacted Chemical Vapor Deposition Grown Monolayer MoS<sub>2</sub> Transistors. *ACS Nano* **2014**, *8*, 5304–5314.

(27) Perkins, F. K.; Friedman, A. L.; Cobas, E.; Campbell, P. M.; Jernigan, G. G.; Jonker, B. T. Chemical Vapor Sensing with Monolayer MoS<sub>2</sub>. *Nano Lett.* **2013**, *13*, 668–673.

(28) Late, D. J.; Huang, Y. K.; Liu, B.; Acharya, J.; Shirodkar, S. N.; Luo, J.; Yan, A.; Charles, D.; Waghmare, U. V.; Dravid, V. P.; Rao, C. N. R. Sensing Behavior of Atomically Thin-Layered  $MoS_2$  Transistors. *ACS Nano* **2013**, *7*, 4879–4891.

(29) Jiang, J.; Dhar, S. Tuning the Threshold Voltage from Depletion to Enhancement Mode in a Multilayer  $MoS_2$  Transistor via Oxygen Adsorption and Desorption. *Phys. Chem. Chem. Phys.* **2016**, 18, 685–689.

(30) Shu, J.; Wu, G.; Gao, S.; Liu, B.; Wei, X.; Chen, Q. Influence of Water Vapor on the Electronic Property of MoS<sub>2</sub> Field Effect Transistors. *Nanotechnology* **2017**, *28*, 204003.

(31) Ahn, J. H.; Parkin, W. M.; Naylor, C. H.; Johnson, A. T. C.; Drndić, M. Ambient Effects on Electrical Characteristics of CVD-Grown Monolayer MoS<sub>2</sub> Field-Effect Transistors. *Sci. Rep.* **2017**, *7*, 4075.

(32) Late, D. J.; Liu, B.; Matte, H. S. S. R.; Dravid, V. P.; Rao, C. N. R. Hysteresis in Single-Layer MoS<sub>2</sub> Field Effect Transistors. *ACS Nano* **2012**, *6*, 5635–5641.

(33) Shimazu, Y.; Tashiro, M.; Sonobe, S.; Takahashi, M. Environmental Effects on Hysteresis of Transfer Characteristics in Molybdenum Disulfide Field-Effect Transistors. *Sci. Rep.* **2016**, *6*, 30084.

(34) Di Bartolomeo, A.; Genovese, L.; Giubileo, F.; Iemmo, L.; Luongo, G.; Foller, T.; Schleberger, M. Hysteresis in the Transfer Characteristics of  $MoS_2$  Transistors. 2D Mater. **2018**, 5, No. 015014. (35) Li, T.; Du, G.; Zhang, B.; Zeng, Z. Scaling Behavior of Hysteresis in Multilayer  $MoS_2$  Field Effect Transistors. Appl. Phys. Lett. **2014**, 105, No. 093107.

(36) Guo, Y.; Wei, X.; Shu, J.; Liu, B.; Yin, J.; Guan, C.; Han, Y.; Gao, S.; Chen, Q. Charge Trapping at the MoS<sub>2</sub>-SiO<sub>2</sub> Interface and its Effects on the Characteristics of MoS<sub>2</sub> Metal-Oxide-Semiconductor Field Effect Transistors. *Appl. Phys. Lett.* **2015**, *106*, 103109.

(37) Cho, K.; Park, W.; Park, J.; Jeong, H.; Jang, J.; Kim, T. Y.; Hong, W. K.; Hong, S.; Lee, T. Electric Stress-Induced Threshold Voltage Instability of Multilayer  $MoS_2$  Field Effect Transistors. *ACS Nano* **2013**, *7*, 7751–7758.

(38) Seo, S. G.; Jin, S. H. Bias Temperature Stress Instability of Multilayered  $MoS_2$  Field-Effect Transistors With CYTOP Passivation. *IEEE Trans. Electron Devices* **2019**, *66*, 2208–2213.

(39) Kim, M. J.; Choi, Y.; Seok, J.; Lee, S.; Kim, Y. J.; Lee, J. Y.; Cho, J. H. Defect-Free Copolymer Gate Dielectrics for Gating MoS<sub>2</sub> Transistors. *J. Phys. Chem. C* **2018**, *122*, 12193–12199.

(40) Illarionov, Y. Y.; Rzepa, G.; Waltl, M.; Knobloch, T.; Grill, A.; Furchi, M. M.; Mueller, T.; Grasser, T. The Role of Charge Trapping in  $MoS_2/SiO_2$  and  $MoS_2/hBN$  Field-Effect Transistors. 2D Mater. 2016, 3, No. 035004.

(41) Illarionov, Y. Y.; Smithe, K. K. H.; Waltl, M.; Knobloch, T.; Pop, E.; Grasser, T. Improved Hysteresis and Reliability of  $MoS_2$ Transistors with High-Quality CVD Growth and  $Al_2O_3$  Encapsulation. *IEEE Electron Device Lett.* **2017**, *38*, 1763–1766.

(42) Park, W.; Pak, Y.; Jang, H. Y.; Nam, J. H.; Kim, T. H.; Oh, S.; Choi, S. M.; Kim, Y.; Cho, B. Improvement of the Bias Stress Stability in 2D  $MoS_2$  and  $WS_2$  transistors with a  $TiO_2$  Interfacial Layer. Nanomaterials **2019**, *9*, 1155.

(43) Cheng, Z.; Cardenas, J. A.; McGuire, F.; Najmaei, S.; Franklin, A. D. Modifying the Ni-MoS<sub>2</sub> Contact Interface Using a Broad-Beam Ion Source. *IEEE Electron Device Lett.* **2016**, *37*, 1234–1237.

(44) McGuire, F. A.; Lin, Y.-C.; Price, K.; Rayner, G. B.; Khandelwal, S.; Salahuddin, S.; Franklin, A. D. Sustained Sub-60 mV/decade Switching Via the Negative Capacitance Effect in MoS<sub>2</sub> Transistors. *Nano Lett.* **2017**, *17*, 4801–4806.

www.acsami.org

(45) Noyce, S. G.; Doherty, J. L.; Cheng, Z.; Han, H.; Bowen, S.; Franklin, A. D. Electronic Stability of Carbon Nanotube Transistors Under Long-Term Bias Stress. *Nano Lett.* **2019**, *19*, 1460–1466.

(46) Yang, S.; Park, S.; Jang, S.; Kim, H.; Kwon, J. Y. Electrical Stability of Multilayer MoS<sub>2</sub> Field-Effect Transistor Under Negative Bias Stress at Various Temperatures. *Phys. Status Solidi RRL* **2014**, *8*, 714–718.

(47) Lee, J. M.; Cho, I. T.; Lee, J. H.; Kwon, H. I. Bias-Stress-Induced Stretched-Exponential Time Dependence of Threshold Voltage Shift in InGaZnO Thin Film Transistors. *Appl. Phys. Lett.* **2008**, 93, No. 093504.

(48) Chen, T. C.; Chang, T. C.; Tsai, C. T.; Hsieh, T. Y.; Chen, S. C.; Lin, C. S.; Hung, M. C.; Tu, C. H.; Chang, J. J.; Chen, P. L. Behaviors of InGaZnO Thin Film Transistor Under Illuminated Positive Gate-Bias Stress. *Appl. Phys. Lett.* **2010**, *97*, 112104.

(49) Mathijssen, S. G. J.; Cölle, M.; Gomes, H.; Smits, E. C. P.; De Boer, B.; McCulloch, I.; Bobbert, P. A.; De Leeuw, D. M. Dynamics of Threshold Voltage Shifts in Organic and Amorphous Silicon Field-Effect Transistors. *Adv. Mater.* **2007**, *19*, 2785–2789.

(50) Mathijssen, S. G. J.; Kemerink, M.; Sharma, A.; Cölle, M.; Bobbert, P. A.; Janssen, R. A. J.; De Leeuw, D. M. Charge Trapping at the Dielectric of Organic Transistors Visualized in Real Time and Space. *Adv. Mater.* **2008**, *20*, 975–979.

(51) Lee, D. W.; Lee, J.; Sohn, I. Y.; Kim, B. Y.; Son, Y. M.; Bark, H.; Jung, J.; Choi, M.; Kim, T. H.; Lee, C.; Lee, N. E. Field-Effect Transistor with a Chemically Synthesized  $MoS_2$  Sensing Channel for Label-Free and Highly Sensitive Electrical Detection of DNA Hybridization. *Nano Res.* **2015**, *8*, 2340–2350.

(52) Hammond, P. A.; Cumming, D. R. S. Encapsulation of a Liquid-Sensing Microchip Using SU-8 Photoresist. *Microelectron. Eng.* **2004**, 73–74, 893–897.

(53) Dankerl, M.; Hauf, M. V.; Lippert, A.; Hess, L. H.; Birner, S.; Sharp, I. D.; Mahmood, A.; Mallet, P.; Veuillen, J. Y.; Stutzmann, M.; Garrido, J. A. Graphene Solution-Gated Field-Effect Transistor Array for Sensing Applications. *Adv. Funct. Mater.* **2010**, *20*, 3117–3124.

(54) Thi, Q. H.; Kim, H.; Zhao, J.; Ly, T. H. Coating Two-Dimensional  $MoS_2$  with Polymer Creates a Corrosive Non-Uniform Interface. 2D Mater. Appl. **2018**, 2, 34.

(55) Park, W.; Park, J.; Jang, J.; Lee, H.; Jeong, H.; Cho, K.; Hong, S.; Lee, T. Oxygen Environmental and Passivation Effects on Molybdenum Disulfide Field Effect Transistors. *Nanotechnology* **2013**, *24*, No. 095202.

(56) Qiu, H.; Pan, L.; Yao, Z.; Li, J.; Shi, Y.; Wang, X. Electrical Characterization of Back-Gated Bi-layer  $MoS_2$  Field-Effect Transistors and the Effect of Ambient on their Performances. *Appl. Phys. Lett.* **2012**, *100*, 123104.

(57) Engelhardt, J.; Hahn, G.; Terheiden, B. Multifunctional ICP-PECVD Silicon Nitride Layers for High-efficiency Silicon Solar Cell Applications. *Energy Procedia* **2015**, *77*, 786–790.

(58) Olziersky, A.; Barquinha, P.; Vila, A.; Pereira, L.; Goncalves, G.; Fortunato, E.; Martins, R.; Morante, J. R. Insight on the SU-8 Resist as Passivation Layer for Transparent Ga<sub>2</sub>O<sub>3</sub>-In<sub>2</sub>O<sub>3</sub>-ZnO Thin-Film Transistors. J. Appl. Phys. **2010**, 108, No. 064505.

(59) Han, Y. J.; Choi, Y. J.; Cho, I. T.; Jin, S. H.; Lee, J. H.; Kwon, H. I. Improvement of Long-Term Durability and Bias Stress Stability in p-Type SnO Thin-Film Transistors Using a SU-8 Passivation Layer. *IEEE Electron Device Lett.* **2014**, 35, 1260–1262.

(60) Illarionov, Y. Y.; Waltl, M.; Rzepa, G.; Kim, J. S.; Kim, S.; Dodabalapur, A.; Akinwande, D.; Grasser, T. Long-Term Stability and Reliability of Black Phosphorus Field-Effect Transistors. *ACS Nano* **2016**, *10*, 9543–9549.

(61) Wood, J. D.; Wells, S. A.; Jariwala, D.; Chen, K. S.; Cho, E.; Sangwan, V. K.; Liu, X.; Lauhon, L. J.; Marks, T. J.; Hersam, M. C. Effective Passivation of Exfoliated Black Phosphorus Transistors Against Ambient Degradation. *Nano Lett.* **2014**, *14*, 6964–6970.

(62) Wang, S.; Zhao, W.; Giustiniano, F.; Eda, G. Effect of Oxygen and Ozone on P-Type Doping of Ultra-Thin WSe<sub>2</sub> and MoSe<sub>2</sub> Field Effect Transistors. *Phys. Chem. Chem. Phys.* **2016**, *18*, 4304–4309.

(63) Song, J. G.; Kim, S. J.; Woo, W. J.; Kim, Y.; Oh, I. K.; Ryu, G. H.; Lee, Z.; Lim, J. H.; Park, J.; Kim, H. Effect of Al<sub>2</sub>O<sub>3</sub> Deposition on Performance of Top-Gated Monolayer MoS<sub>2</sub>-Based Field Effect Transistor. *ACS Appl. Mater. Interfaces* **2016**, *8*, 28130–28135.