# Cite This: Nano Lett. 2019, 19, 5077–5085

# Immunity to Contact Scaling in MoS<sub>2</sub> Transistors Using in Situ Edge Contacts

Zhihui Cheng,<sup>†</sup><sup>®</sup> Yifei Yu,<sup>‡</sup> Shreya Singh,<sup>†</sup> Katherine Price,<sup>†</sup><sup>®</sup> Steven G. Noyce,<sup>†</sup> Yuh-Chen Lin,<sup>†</sup> Linyou Cao,<sup>‡</sup><sup>®</sup> and Aaron D. Franklin<sup>\*,†,§</sup><sup>®</sup>

<sup>†</sup>Department of Electrical and Computer Engineering, Duke University, Durham, North Carolina 27708, United States <sup>‡</sup>Department of Materials Science and Engineering, North Carolina State University, Raleigh, North Carolina 27695, United States <sup>§</sup>Department of Chemistry, Duke University, Durham, North Carolina 27708, United States

Supporting Information

**ABSTRACT:** Atomically thin two-dimensional (2D) materials are promising candidates for sub-10 nm transistor channels due to their ultrathin body thickness, which results in strong electrostatic gate control. Properly scaling a transistor technology requires reducing both the channel length (distance from source to drain) and the contact length (distance that source and drain interface with semiconducting channel). Contact length scaling remains an unresolved epidemic for transistor scaling, affecting devices from all semiconductors—silicon to 2D materials. Here, we show that clean edge contacts to 2D MoS<sub>2</sub> can provide immunity to the contact-scaling problem, with performance that is independent of contact length down to the 20 nm regime. Using a directional ion beam, in situ edge contacts of various metal—MoS<sub>2</sub> interfaces are studied. Characterization of the intricate edge interface using cross-sectional electron microscopy reveals distinct morphological effects on the MoS<sub>2</sub> depending on its thickness—from monolayer to few-layer films. The in situ edge contacts also exhibit an order of magnitude higher performance compared to the best-reported ex situ metal

edge contacts. Our work provides experimental evidence for a solution to contact scaling in transistors, using 2D materials with clean edge contact interfaces, opening a new way of designing devices with 2D materials.

KEYWORDS: 2D materials, in situ edge contacts, contact scaling, splitting 2D crystals, metal-2D interfaces

**B** ooming applications, such as smartphones, autonomous vehicles, and server farms, leave society starving for more computational power. At the heart of virtually all computation is the transistor, which yields increased computational ability with each successive technology node through size scaling. Such scaling, which enjoyed decades of success predicted by Moore's law, is now undisputedly slowing and potentially reaching an end based on the limitations of silicon.<sup>1–5</sup> Not surprisingly, the electronic device community has been eager to explore new materials for the transistor channel that may extend the scalability roadmap, even for a few more generations. Nanomaterials have long been seen as a viable option, from 1D carbon nanotubes to the expanding family of 2D crystals. For 2D, graphene initially captured widespread attention and spawned a whole library of 2D materials with a variety of electronic band structures and properties.<sup>6–11</sup>

The main advantage of 2D materials is their ultrathin nature, which could enable extremely scaled transistors for the "Beyond Moore" era. The ultrathin body thickness directly affects the screening length, which dictates how short the channel length can be scaled down without inducing deleterious short channel effects. Using a planar device structure, it is estimated that monolayer  $MoS_2$  has a screening length of less than 1 nm,<sup>12</sup> assuming an equivalent oxide

thickness (EOT) of 1 nm is used. This suggests that the gatetunable, 2D-based transistor can be scaled to sub-5 nm channel length—a scale where Si encounters severe short channel effects using similar gate structures. Both experimental and theoretical studies have demonstrated the superb channel length scalability of 2D field-effect transistors (FETs).<sup>12–18</sup> Aside from the superior scalability, 2D materials also offer new possibilities for other unconventional applications (for example, flexible electronics) because of their substrate independence.<sup>19–21</sup> Moreover, a plethora of atomic heterostructures can be formed between different 2D materials,<sup>22–26</sup> in a way that is inaccessible to traditional semiconductors.

While the scalability of channel length in 2D FETs has been well studied,<sup>13-15,17,18,27</sup> the contact length and its related scaling challenges have been largely neglected. However, contact engineering in general for 2D FETs has been a topic of discussion,<sup>28-31</sup> as well as using different metals,<sup>32,33</sup> transforming phases,<sup>34</sup> and interface engineering.<sup>11,35</sup> While these approaches deepen our understanding of the metal–2D interface and have achieved contact resistance as low as 200

Received:

April 2, 2019

Revised:

June 11, 2019

Published:

July 8, 2019

$\Omega$ - $\mu$ m, they all use a contact length of at least hundreds of nanometers, which is orders of magnitude larger than needed for actual technologies. A fully scaled device technology for the 2030 era will require both the channel and contact lengths to scale below 12 nm (equivalent to a contacted gate pitch of 24 nm).<sup>36</sup> Note that contact scaling is also a pressing challenge for traditional Si technology. In a Si FinFET, the contact length (36 nm) occupies two-thirds of the gate pitch (54 nm for Intel's 10 nm node technology).<sup>37</sup> Since future scaled transistors (including traditional Si-based devices) would have a shorter gate pitch, the shrinking gate pitch also leads to shrinking contact length, thus decreasing on-state performance<sup>38</sup> and highlighting the importance of contact scaling. In a simplified top-contacted and back-gated MoS<sub>2</sub> transistor, as shown in Figure 1a, as the contact length ( $L_c$ ) decreases, the

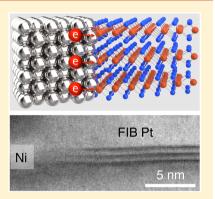

**Figure 1.** Top versus edge contacts to 2D MoS<sub>2</sub>. (a) Schematic of a bilayer 2D FET with traditional top contacts. (b) On-current diminishes as the top contact length decreases (data from ref 35), presenting a major roadblock for aggressively scaled transistors. Transfer length is indicated in inset schematic. (c) Schematic of a bilayer 2D FET with edge contacts and an effective  $L_c \approx 1$  nm, leading to the possibility of (d) on-current that is independent of contact length. The on-current values in panel (d) are hypothetical.

area available for carrier injection is also reduced. The shrinking contact length leads to severely degraded performance, especially when  $L_c$  drops below the transfer length ( $L_T = 30-40$  nm for MoS<sub>2</sub>,<sup>35</sup> as depicted in Figure 1b), which is the length over which the majority of carriers are injected.

Ideally, for scaling, contacts would be bonded directly to the side of the 2D channel as pure "edge contacts," as illustrated in Figure 1c, where charge is injected from the metal directly into the 2D crystal via covalent bonds. Since the area of injection at the edge is independent of the physical contact length, we hypothesize that edge contacts could provide ultimate scalability, as shown hypothetically in Figure 1d, where the on-current  $(I_d)$  would be independent of the  $L_c$ . Several studies on edge contacts to 2D materials have been reported, beginning with Cr edge contacts to graphene that exhibited a low contact resistance of 150  $\Omega$ · $\mu$ m,<sup>39</sup> though graphene is not a semiconductor. A decade before MoS<sub>2</sub> was considered as a transistor channel material, MoS<sub>2</sub> edges were explored, with results indicating that one-dimensional metallic states can be identified due to the band structure changes significantly at the edge.<sup>40</sup> In a separate study,<sup>41</sup> an edge-like contact interface between graphene and MoS<sub>2</sub> was demonstrated; however, the

$MoS_2$ -graphene junction spans ~20 nm and the scalability of this approach is uncertain. Moreover, growing the graphene-MoS<sub>2</sub> edge added additional complexity and variability to the fabrication process, reducing the reliability of this approach. Hybrid top and edge contacts have been proposed,<sup>42,43</sup> but the current crowding effect caused by the application of  $V_{ds}$  at the contact promotes carrier injection through the top contact interface instead of the edge interface, casting doubt on whether the edge contact interfaces are providing any real benefit. Finally, demonstration of edge contacts between metal and MoS<sub>2</sub> has been limited to the use of an ex situ and isotropic plasma etching approach.<sup>44</sup> The performance metrics such as on-current and on-off ratio were unfavorable, possibly due to the uncleanliness of the interface with the dangling bonds in the exposed MoS<sub>2</sub> edge reacting with species in the ambient owing to the use of an ex situ plasma etching. Considering the ultrasensitive nature of the dangling bonds at the edge, it is thus crucial to have the interface preserved in a clean in situ environment in order to properly determine the potential of metal-MoS<sub>2</sub> edge contacts.

Here, we demonstrate edge-contacted  $MoS_2$  FETs by using an *in situ* Ar ion beam. We show the ultimate scalability of pure edge contacts to CVD-grown  $MoS_2$  of various layer thicknesses and metal types, providing evidence for the immunity of edgecontacted 2D FETs to aggressive contact scaling. In order to understand carrier transport at the edge interface, we use crosssectional scanning transmission electron microscopy (STEM) and low-temperature electrical measurement to characterize the edge contacts. Our study elucidates the intriguing metal– 2D edge interface and the potential of edge contacts for future scaled transistors.

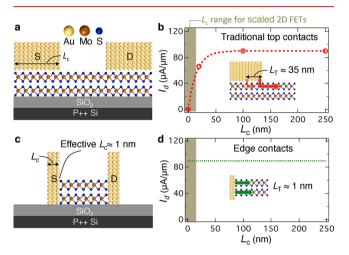

Etching Capability of a Directional Ar Ion Beam. The use of an *in situ* ion beam to etch the MoS<sub>2</sub> immediately prior to contact metallization is crucial to avoid reactivity between the created edge states and molecular species other than the contact metal. The in situ ion beam source is incorporated with an electron beam evaporator in the same ultrahigh vacuum (UHV) chamber, as shown in Figure 2a. The etching effect of the ion beam on  $MoS_2$  is studied using the process shown in Figure 2b. Selective bombardment of the exposed (contact) regions by the directional Ar ion beam is achieved using patterned PMMA (which shields the channel regions). Note that the Ar ion beam has a minimal etching effect on the PMMA, which make PMMA a suitable etch mask, as shown in Figure S6. Our previous study<sup>45</sup> shows that low-energy ( $\sim 100$ eV) Ar ion bombardment can create vacancies in the 2D crystal. Here, a higher energy (~600 eV) ion beam is shown to controllably etch the MoS<sub>2</sub>, as shown in the atomic force microscopy (AFM) image in Figure 2c. We also use energy dispersive spectroscopy (EDS) to map the etched flake in Figure 2c. The sulfur signal in Figure 2d and molybdenum signal in Figure 2e further prove the etching capability of the Ar ion beam. The AFM profiles and line scans from different regions show how both the MoS<sub>2</sub> and SiO<sub>2</sub> are etched by the ion bombardment, as plotted in Figure 2f. Note that the edge of MoS<sub>2</sub> in the etched region attracts more reacted species/ residue (as high as 100 nm in Figure 2g) compared to the  $SiO_2$ etched edge, evidential of the higher reactivity of the MoS<sub>2</sub> edge when exposed to solvent/air (ex situ) and the importance of forming edge contacts with an in situ process. Meanwhile, the flake edge that has not been exposed to the ion beam is relatively clean, as shown in Figure 2g. This further exemplifies the highly reactive etched edge, which could be useful in other

**Figure 2.** In situ etching of  $MoS_2$ . (a) Ion beam source and e-beam evaporator incorporated within the same UHV chamber. (b) Schematic of the etch process with only contact regions selectively bombarded by Ar ion beam. (c) AFM image of  $MoS_2$  flake after etching and PMMA removal. EDS mapping of the flake in panel (c) gives the sulfur signal in panel (d) and molybdenum signal in panel (e). (f) Line scan height profiles 1 and 2 from the AFM image in panel (c). (g) Three-dimensional AFM image of panel (c) highlighting the reactive etched  $MoS_2$  edges and the relatively clean  $MoS_2$  flake edges.

applications such as sensing. The edge sites could act as a preferable binding site for antibodies compared to either the basal surface that has limited dangling bonds or the natural edges that are less reactive. In Figure 2g, we also label the  $SiO_2$  and  $MoS_2$  etched depth shown in Figure 2f. The relationship between the etch-depth and the ion beam exposure time is plotted in Figure S7.

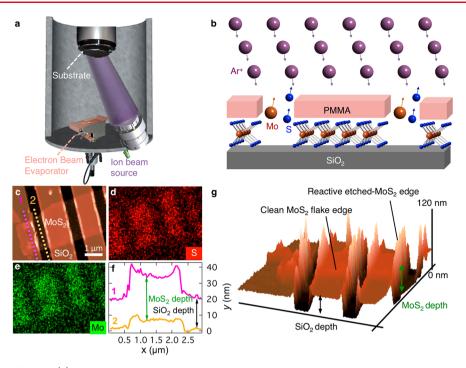

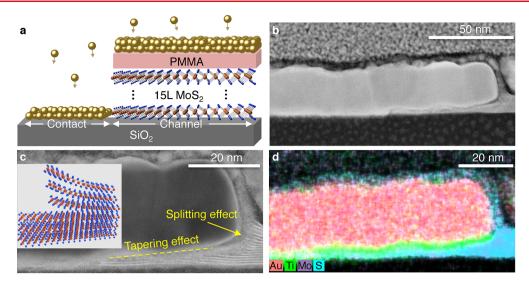

Edge Contacts to Exfoliated Multilayer MoS<sub>2</sub>. Upon exposing the  $MoS_2$  edge in the contact regions under UHV, contact metal is then deposited using an electron beam evaporator in the same chamber. The newly generated edge states are able to react with the depositing metal, forming a bonded edge interface. To study this interface, we use crosssectional scanning tunneling electron microscopy (STEM) to characterize the etched edge. Fifteen layers of MoS<sub>2</sub> were exfoliated onto a silicon wafer with 300 nm SiO<sub>2</sub> (see crosssectional STEM image in Figure S8). After using the etching process illustrated in the last section, the metal contact was in situ deposited on the etched region (Figure 3a). The crosssectional STEM image of the finished contact is shown in Figure 3b. The etching process creates the unique splitting and tapering effects (Figure 3c), which is particularly surprising as these effects are different from the common undercut<sup>46</sup> and microtrench<sup>47</sup> profile seen in some isotropic ex situ plasma processes. The splitting effect could be attributed to the interaction between the directional Ar ion beam and the weak van der Waals interlayer binding of the 2D materials. The splitting effect could profoundly change electronic properties of the  $MoS_2$  at the edge (further details in Note S1). Meanwhile, the tapering effect is common for directional dry etching,<sup>48</sup> as the center region receives more directional ion bombardment. These effects open a new window of opportunities to study the intricate interface between metal

and 2D materials and to use in other applications such as sensing and material intercalation.  $^{\rm 49-51}$

To further understand the metal—MoS<sub>2</sub> edge interface, EDS was used to characterize the elements present in the right-side edge of the contact. As shown in Figure 3d, the MoS<sub>2</sub> is topped with 2 nm of Ti (green) and 20 nm of Au (red). The thickness of Ti is more uniform in the area where there is more MoS<sub>2</sub> edge in the splitting and tapering region, indicative of more consistent bonding because of the reactive edge states. The combined elemental map shown in Figure 3d may suggest that sulfur is concentrated at the splitting interface, but the individual sulfur map in Figure S9 shows that the distribution of sulfur within the metal region after etching is actually quite even. Also, the oxygen was mapped in Figure S9, and no higher concentration appears in the interface between Ti and MoS<sub>2</sub>, which suggests that the *in situ* environment is relatively pristine.

In addition to the interface highlighted in Figure 3, where the full multilayer MoS<sub>2</sub> is etched by the Ar ion beam in the center of the contact regions (quasi-edge contacts), we also used shorter etching time (25 and 50 s) to produce partially etched MoS<sub>2</sub> in the center of the contact region (partial-edge contacts), as given in Figure S10. Since the exfoliated flake is about 10 nm thick (15L), the tapering and splitting effects in Figure 3 also show up in the partial-edge contacts. We then fabricated devices on multilayer flakes with different thickness (35 and 8 nm) in order to compare performance of the quasiedge and partial-edge contacts (see Notes S1-S2). Compared to the partial-edge contacts (9  $\mu$ A/ $\mu$ m at V<sub>ds</sub> = 1 V), quasiedge contacts yield smaller current (5  $\mu$ A/ $\mu$ m at V<sub>ds</sub> = 1 V) but have a distinct forming or "burn-in" effect when large  $V_{ds}$  (over 3 V) is applied. This forming behavior suggests that a large electric field from source to drain can strengthen the bond

Figure 3. Metal edge interface to multilayer MoS<sub>2</sub> flakes. (a) Diagram of the *in situ* metal deposition process forming an edge contact for 15L MoS<sub>2</sub> flake with 2 nm Ti/20 nm Au. (b) Cross-sectional STEM image of  $L_c = 200$  nm contact. (c) Magnification of left edge of the contact showing tapering and splitting effects. Inset image showing the splitting effect for MoS<sub>2</sub> crystal. (d) EDS image of right side of the contact mapping the presence of different elements.

between the metal and  $MoS_2$  edge states. Considering that the defects created on the tapering region add additional complications to the analysis, further investigation is needed to resolve the carrier injection through the splitting  $MoS_2$  edge and the tapering layers. In the following section, in order to demonstrate pure edge contacts and their scaling behavior, we focus on CVD-grown  $MoS_2$  films since they offer a large area of thin crystals (1–4 layers with size of over 100  $\mu$ m<sup>2</sup>).

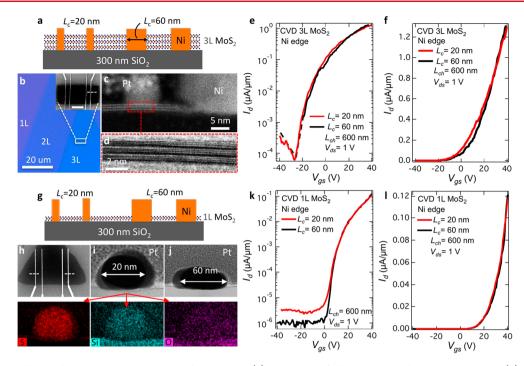

Edge Contacts to CVD-Grown MoS<sub>2</sub> (As Grown on SiO<sub>2</sub>). In order to demonstrate the ultimate scalability of edge contacts, in situ edge contacts were fabricated on CVD-grown MoS<sub>2</sub>. These MoS<sub>2</sub> films have a large area with uniform thickness, making them suitable for device fabrication and performance comparison. Trilayer and monolayer CVD films were used to fabricate in situ edge contacts as shown in Figure 4. These films were grown directly onto SiO<sub>2</sub> without the need of a transfer process, which could introduce contaminants such as water molecules and resist residue. In Figure 4a, a small rectangular box of MoS<sub>2</sub> was used, as the materials outside of the rectangular box are etched away using CF<sub>4</sub> plasma. After an e-beam lithography process, the same Ar ion beam etching process to Figure 2b with an etching time of 30 s was used and the contact metal (Ni) was deposited in situ inside the same UHV chamber. A diagram of scaled edge contacts to MoS<sub>2</sub> is given in Figure 4b, where two long contacts ( $L_c = 60 \text{ nm}$ ) and two short contacts ( $L_c = 20 \text{ nm}$ ) were fabricated onto the same film. The cross-sectional STEM image of the right-side of the  $L_c = 60$  nm edge contacts is shown in Figure 4c. The metal entrenches into the oxide and contacts the edge of the trilayer film without the splitting effect, producing pure edge contacts. The side-view of the three-layer MoS<sub>2</sub> film with atomic resolution is given in Figure 4d, showing the crystal structure of the 2D material. Characterization of the devices with different contact lengths (Figure 4e,f) revealed that the  $L_c = 20$ nm and  $L_c = 60$  nm FETs have the essentially same  $I_{d}$ , independent of the contact length. One of the most encouraging aspects of this result is the sheer density of carriers being injected into the edge contact area (effective  $L_c$  = 1 nm), which is over an order of magnitude smaller than the

top contact  $L_c$  using the same film and 2 orders of magnitude smaller than the top contact  $L_c$  used in other studies.

Edge contacts to monolayer MoS<sub>2</sub> from CVD-grown crystals were also explored. A device structure similar to the one illustrated in Figure 4a was used, with monolayer MoS<sub>2</sub> as the channel material (Figure 4g). A triangular monolayer film was chosen, and the same process of in situ etching and metal evaporation was used to make the edge contacts with different contact lengths. The cross-sectional STEM images show the metal entrenching into the oxide, representative of complete MoS<sub>2</sub> removal in the contact region. To avoid damaging the bottom oxide, shorter exposure time can be used. In Figure S12, we used 5 s of 600 eV Ar ion beam and found that 2L MoS<sub>2</sub> can be etched. No significant aspect ratio-dependent etching was observed from our study using directional ion beam etching compared to traditional plasma etching.<sup>52</sup> Additionally, our recent study shows that 3 s of 60 and 200 eV Ar ion beam are capable of etching away 1L MoS<sub>2</sub>.<sup>53</sup> Hence, the damage to the bottom  $SiO_2$  should be minimal considering the short exposure time (see Figure S7 for reference). EDS images of the contact (Figure 4i) provide further evidence of the isolation of the MoS<sub>2</sub> to the channel and the abrupt contact interface. A magnified view of the sulfur at the edge is given in Figure S11, further showing this abrupt cutoff of the monolayer MoS<sub>2</sub> at the edge. The corresponding  $I_{\rm d} - V_{\rm gs}$  curves for the monolayer MoS<sub>2</sub> devices are given in Figure 4k-l. The corresponding  $I_d - V_{gs}$  curves for the monolayer  $MoS_2$  devices are given in Figure 4k-l. The difference in the off-current in Figure 4k is attributed to deviceto-device variation as no clear relationship between off-current and contact length was observed. Possible explanations for the low performance observed in the edge-contacted 1L MoS<sub>2</sub> will be discussed in coming sections.

The effect of different metal types is also important in understanding the in situ edge contact scheme. The I-V characteristics of Au, Cr, and Ni are compared in Figure S13. After shifting  $V_{th}$ , Cr yields similar performance compared to Ni. This result is in contrast to the previous study where Cr is shown to outperform the other metals when contacting graphene through the edge,<sup>39</sup> which indicates the edge contact

**Figure 4.** Trilayer and monolayer  $MoS_2$  FETs with Ni edge contacts. (a) Schematic of edge-contacted devices on 3L  $MoS_2$ . (b) Optical image of CVD-grown flakes with inset SEM image of trilayer  $MoS_2$  FETs; scale bar in SEM image is 1  $\mu$ m. Cross-sectional STEM images of (c) right edge of  $L_c = 60$  nm contact and (d) atomic side-view of the trilayer  $MoS_2$ . (e) Subthreshold and (f) transfer characteristics of the edge-contacted devices, showing performance that is independent of contact length. (g) Schematic of edge-contacted devices on monolayer  $MoS_2$ . (h) SEM image of the devices with a scale bar of 1  $\mu$ m. STEM images of (i)  $L_c = 20$  nm contact and (j)  $L_c = 60$  nm contact. Arrows point to corresponding EDS scans of sulfur, silicon, and oxygen in panel (i). (k) Subthreshold and (1) transfer characteristics of the monolayer edge-contacted devices, also showing the performance that is independent of contact length.

performance is dependent on the 2D materials properties. Theoretically, Cr has been proposed to be an ideal metal to contact MoS<sub>2</sub> in the top contact scheme, with its shorter bond length to S, larger binding energy, and larger density of state at  $E_{\rm F}$ .<sup>54</sup> As the bonding length could be shorter in the edge contact scheme, density functional theory (DFT) calculations on Cr edge contacts to MoS<sub>2</sub> remain to be conducted in order to confirm the orbital overlapping profile. To further understand the in situ edge contact, we characterized Cr edge contacts under low-temperatures. As given in Note S5, a relatively small Schottky barrier height of 11.7 meV is extracted. Note that the exact barrier profile may be different from traditional top contacts due to the different bandgap at the termination of MoS<sub>2</sub> in addition to different carrier injection mechanism. A focused theoretical study is warranted to investigate the impact of edge interfaces on the band structure and carrier transport of metal-2D edge contacts.

The performance of the edge contacts discussed above is lower than that previously reported for top contacts using the same contact metals.<sup>45,55</sup> From the data presented thus far, one might conclude that edge contacts inherently lead to lower performance due to the decreased area for carrier injection at the edge interface compared to a top contact interface. Alternatively, the quality of the CVD as-grown MoS<sub>2</sub> could be relatively poor considering the likely high density of interface traps formed between SiO<sub>2</sub> and MoS<sub>2</sub> during the hightemperature CVD growth process. To investigate which factor plays a major role, we fabricated both top- and edge-contacted devices on the same as-grown 1L MoS<sub>2</sub>. The device performance (plotted in Figure S14) shows that the top- and edge-contacted devices demonstrate similar performance, indicating that the quality of the as-grown MoS<sub>2</sub> film could be the major factor limiting the performance of the devices presented above. Hence, in the following section, we use transferred  $MoS_2$  rather than as-grown  $MoS_2$  for the channel material.

Scaling Edge Contacts to CVD-Grown MoS<sub>2</sub> (Transferred onto SiO<sub>2</sub>). Devices fabricated on as-grown MoS<sub>2</sub> suffer from low performance and high variability.<sup>56</sup> As mentioned previously, the reason behind the inferior devices could be the higher density of interface traps between the MoS<sub>2</sub> and the SiO<sub>2</sub> substrate. These interface traps can be induced by the high-temperature CVD process.<sup>56</sup> To address this issue, we transferred SiO<sub>2</sub>-grown MoS<sub>2</sub> onto a fresh SiO<sub>2</sub> surface using a water-assisted transfer technique.<sup>57</sup> Ni topcontacted devices were fabricated both on the as-grown MoS<sub>2</sub> and the transferred MoS<sub>2</sub> for comparison. Devices with transferred MoS<sub>2</sub> yield higher performance and smaller variability (Figure S15), consistent with ref 56.

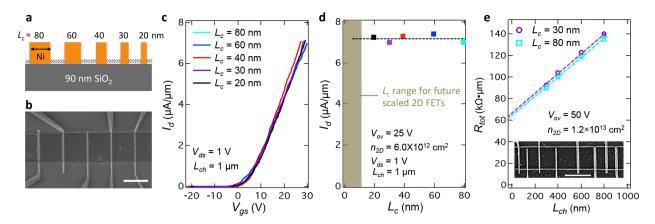

The contact length for edge contacts was varied to determine the scalability of the edge contact scheme. On a transferred CVD-grown 1L MoS<sub>2</sub> film, *in situ* Ni edge contacts were fabricated with different contact lengths, while the channel length remained constant (Figure 5a). The  $I_d-V_{gs}$  curves of the Ni edge contacts with different  $L_c$  are plotted in Figure 5b. The devices with different  $L_c$  have a similar  $I_d-V_{gs}$  profile, indicative of the true edge profile and pure edge injection of carriers since there is invariance with contact length change, as plotted in Figure 5d. Of note is that the performance achieved is 70 times higher than the device built on as-grown MoS<sub>2</sub>. The  $I_d-V_{ds}$  curves in Figure S16 show a slight nonlinearity in the low  $V_{ds}$  regime, suggesting a slight barrier for carrier injection in the edge contacts, we fabricated

**Figure 5.** Scaling of contact length for in situ edge contacts. (a), Device schematics of the scaled Ni edge contacts to 1L MoS<sub>2</sub> FETs. (b) SEM image of the devices in panel (a). Scale bar, 1  $\mu$ m. (c) Example transfer curves of edge-contacted devices. (d) Relationship between  $I_d$  and  $L_c$  for in situ edge contacts after aligning the  $V_{th}$  in panel (c), showing potential for sustaining performance while scaling contact length. (e) TLM structures of edge contacts with different contact length on the same 2L MoS<sub>2</sub> film. Scale bar, 1  $\mu$ m. The 600 eV Ar ion beam exposure time is 5 s.

transfer length model (TLM) structures with different contact length on the same MoS<sub>2</sub> film (see inset of Figure 5e). Example  $I_d - V_{ds}$  curves of the TLM devices are plotted in Figure S17. The total resistances are obtained at  $n_{2D} = 1.2 \times 10^{13}$  cm<sup>2</sup> and at small  $V_{ds}$  value of 0.54 V. The extracted contact resistances for edge contacts with  $L_c = 30$  nm is ~31 k $\Omega \cdot \mu m$ , whereas for  $L_c = 80$  nm, the contact resistance is slightly smaller at ~30.5 k $\Omega \cdot \mu m$ . This small difference between 30 and 80 nm contact length can be attributed to the slightly larger resistance of contact leads for shorter contact length (see Figure S18). The  $R_{tot}$  and  $R_c$  observed is 1 order of magnitude smaller than the best reported edge contacts in the literature (see comparison in Table S1). This improvement comes from the optimization of exposure time, the in situ UHV environment, and the transferred MoS<sub>2</sub> film.

Directly comparing these in situ edge-contacted 2D FETs with the other reported ex situ edge contacts can be difficult considering that parameters such as the carrier density, channel length, and film quality all need to be taken into account<sup>30</sup> (see Table S1). However, based on devices with similar carrier density and channel length, the in situ Ni edge contacts outperform the best-reported ex situ metal-MoS<sub>2</sub> edge contacts by an order of magnitude. This improvement could be associated with the different metal types, the directional ion beam etching and in situ metal deposition. Combined with the scaling result plotted in Figure 5c-e, the in situ Ni edge contacts demonstrate significant advances for better edge contacts to semiconducting 2D materials and show the ability for edge contacts to provide immunity to scaling in future scaled 2D FETs. Further work is needed to study contact lengths smaller than 20 nm, where the yield of metal contacts is low depending on the e-beam lithography tools and processes. As metal lines are scaled down to the width of single grains, other undesirable features begin to appear, such as ridges, valleys, and grain boundaries.<sup>58</sup> These effects will impact top contact performance more than edge contacts, as the top contact interfaces become nonsmooth, thus impacting the interfacial contact area. Research in this aspect remains scarce and merits further investigation.

One additional consideration is the resistance of scaled contact leads and their impact on device performance; the smaller the metal contact (in terms of  $L_c$ ), the larger the resistance. We used two pads to connect each of the metal

contacts in order to obtain the resistance of the contact leads, from the pads to the thin metal line (see Figure S18 for details). As  $L_c$  decreases from 80 to 20 nm, the resistance increases ~30%, from 950  $\Omega$  to 1230  $\Omega$ . However, this resistance is far smaller than the total resistance of the device, thus its impact is negligible for the overall device performance. For future ultrascaled devices, where the contact resistance and the channel resistance have been reduced to a few hundred ohms, the resistance of the contact metal leads should be taken into account and studied explicitly.

Overall, while the top contacts can outperform in situ edge contacts at long contact lengths of  $L_c > 20$  nm, attention should be given to the short contact length where the 2D materials would most likely be utilized in future scaled transistors. Furthermore, now that edge contacts to a 2D semiconductor have been demonstrated, continued study and optimization will improve their quality and resulting device performance. Further investigations may include (1) exploring more metal types to find a preferable edge interface; (2) doping the contact region before fabricating the edge contacts to further increase the number of carriers injected to the flake through the edge and thus decrease the contact resistance;<sup>59</sup> and (3) combining with shorter channel length to demonstrate edge-contacted, short-channel devices.

**Conclusion.** In situ edge contacts to MoS<sub>2</sub> FETs were demonstrated to provide immunity to contact length scaling for future generation devices. The challenge of preserving and utilizing the exposed, reactive edge of the MoS<sub>2</sub> was overcome by using in situ ion beam etching with contact metal deposition. The performance of the transistors remained consistent even as  $L_c$  ranged from 20 to 60 nm across a set of devices, experimentally demonstrating that edge contacts are advantageous for ultimate 2D contact scaling. Moreover, the comparison of edge contacts versus top contacts was demonstrated and the impact of different metals (Ni, Cr, and Au) was explored using the same edge contact scheme. Further theoretical and experimental investigations are warranted to better understand the edge contact interface and decrease the contact resistance. Our work sheds light on the potential of edge contacts for ultimate contact scaling in MoS<sub>2</sub> transistors and could be applied to other 2D materials and nanoelectronic devices, paving the road for future aggressively scaled devices.

**Methods.** *CVD Growth of the*  $MoS_2$ . The  $MoS_2$  flakes were grown using a chemical vapor deposition (CVD) process reported previously.<sup>60–62</sup> Typically, 1 g of sulfur powder (Sigma-Aldrich) and 15–30 mg of MoO<sub>3</sub> (99.99%, Sigma-Aldrich) source material were placed upstream and at the center of a tube furnace, respectively. The substrates (heavily doped Si substrate with 300 nm SiO<sub>2</sub>) were placed downstream in the furnace tube. Typical growth was performed at 750 °C for 10 min under a flow of Ar gas in rate of 100 sccm and ambient pressure.

Fabrication of in Situ Edge-Contacted Devices. For devices using exfoliated flakes, multilayer MoS<sub>2</sub> flakes were mechanically exfoliated onto a heavily doped Si substrate with 300 nm SiO<sub>2</sub>. For devices using CVD-grown MoS<sub>2</sub> films, the MoS<sub>2</sub> crystal was grown using the above process. For as-grown CVD MoS<sub>2</sub>, the SiO<sub>2</sub> and the MoS<sub>2</sub> assembly coming out of the CVD furnace will be used for the subsequent device patterning. For transferred CVD MoS<sub>2</sub>, an additional transfer process is needed.<sup>57</sup> EBL with PMMA was used to define the contact regions, leads, and pads. The substrate was then developed in a solution of IPA/MIBK= 3:1. After developing, the substrate was transferred to the UHV chamber (base pressure  $\approx 10^{-8}$  Torr) having an ion beam source (KDC 40, KRI) in situ with an e-beam evaporator. The chip was exposed with a 600 eV directional Ar ion beam, followed by metal deposition. A top Au layer (30 nm) is also in situ deposited on top of the in situ Ni and Cr metal (normally 15 nm) to prevent oxidation of the contacts when exposed to ambient. This in situ ion beam process with metal deposition is crucial for protecting the exposed edges from other molecules in the ambient environment. Finally, the fabricated devices were characterized in dry N2 after lift-off in acetone at a temperature of 80 °C.

*Low-Temperature Measurement.* The sample was loaded into Lakeshore probe station (CRX-6.5 K) and was cooled to base temperature (7 K) using a helium compressor (HC-4E1). The temperature was then increased gradually to 30, 50, 80, 140, 200, 250, and 300 K. The measurement was conducted at each temperature.

Characterization of the Edge Contact Interface. The AFM images in Figure 2 were taken from a Digital Instruments Dimension 3100. The SEM images are obtained using an FEI XL30 SEM-FEG. The EDS images in Figure 3 are obtained from a Bruker XFlash 4010 EDS. The cross-sectional STEM images in Figures 3 and 4 were prepared by using an FEI (Thermo-Fisher) Quanta 3D dual beam. A 250 nm coating of electron beam deposited Pt was deposited over the device followed by a 2  $\mu$ m ion beam Pt deposition. Initial lift-out was performed with a 30 kV Ga beam, while final thinning was performed at 16 kV to reduce damage. The final polish of 48 pA at 5 kV was performed at  $\pm 4^{\circ}$  to limit further damage. The STEM images were obtained using FEI Titan 80-300 probe aberration corrected STEM operated at 200 kV. The beam convergence angle was set to 20 mrad, and collection angles >50 mrad were used to obtain the Z-contrast high-angle annular dark-field (HAADF) images. The EDS images in Figures 3 and 4 were acquired from the SuperX system with the four Bruker Silicon Drift Detectors (SDD).

# ASSOCIATED CONTENT

#### **S** Supporting Information

The Supporting Information is available free of charge on the ACS Publications website at DOI: 10.1021/acs.nano-lett.9b01355.

Details on partial- and quasi-edge contacts to exfoliated multilayer  $MoS_2$ , low-temperature characterization of *in situ* Cr edge contacts, benchmarking of metal edge contacts, comparison of  $L_T$  and  $R_c$  component for top and edge contacts, cross-sectional images of  $MoS_2$  with different etching time, and EDS mapping of individual element, comparison of various devices, and resistance of metal contacts with small  $L_c$  (PDF)

#### AUTHOR INFORMATION

#### **Corresponding Author**

\*E-mail: aaron.franklin@duke.edu.

#### ORCID 🔍

Zhihui Cheng: 0000-0003-1285-0523 Katherine Price: 0000-0001-6120-0020 Linyou Cao: 0000-0002-7834-8336 Aaron D. Franklin: 0000-0002-1128-9327

# Author Contributions

Z.C. and A.D.F. designed the experiments. Z.C. fabricated and characterized all the devices. Y.Y. grew the  $MoS_2$  using CVD. S.S. helped characterize the devices. K.P. helped gather some early stage data. S.G.N. helped interpret the EDS data. Z.C. and A.F. wrote the main paper and the Supporting Information with input from all other authors.

# Notes

The authors declare no competing financial interest.

## ACKNOWLEDGMENTS

This work is supported by National Science Foundation (NSF) under Grant ECCS 1508573. Y.Y. and L.C. acknowledge the support of ECCS-1508856 from the National Science Foundation. The authors would like to thank the staff members in the Shared Instrument and Manufacturing Facilities (SMIF) at Duke for their assistance, Roberto Garcia for STEM sample preparation, and Rohan Dhall for obtaining the STEM images in the Analytical Instrumentation Facility (AIF) at NCSU.

### REFERENCES

(1) Khan, H. N.; Hounshell, D. A.; Fuchs, E. R. H. Science and Research Policy at the End of Moore's Law. *Nat. Electron.* **2018**, *1* (1), 14–21.

(2) Mack, C. A. Fifty Years of Moore's Law. *IEEE Trans. Semicond. Manuf.* **2011**, *24* (2), 202–207.

(3) Franklin, A. D. Nanomaterials in Transistors: From High-Performance to Thin-Film Applications. *Science* **2015**, *349* (6249), aab2750.

(4) Waldrop, M. More Than Moore. Nature 2016, 530, 144-147.

(5) Mack, C. The Multiple Lives of Moore's Law. *IEEE Spectrum* **2015**, 52 (4), 31–37.

(6) Novoselov, K. S.; Mishchenko, A.; Carvalho, A.; Castro Neto, A. H. 2D Materials and van Der Waals Heterostructures. *Science* **2016**, 353 (6298), aac9439.

(7) Miro, P.; Audiffred, M.; Heine, T. An Atlas of Two-Dimensional Materials. *Chem. Soc. Rev.* **2014**, *43* (18), 6537–6554.

(8) Xu, M.; Liang, T.; Shi, M.; Chen, H. Graphene-Like Two-Dimensional Materials. *Chem. Rev.* 2013, 113 (5), 3766–3798. (9) Gupta, A.; Sakthivel, T.; Seal, S. Recent Development in 2D Materials beyond Graphene. *Prog. Mater. Sci.* **2015**, *73*, 44–126.

(10) Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Single-Layer  $MoS_2$  Transistors. *Nat. Nanotechnol.* **2011**, 6 (3), 147–150.

(11) Lee, S.; Tang, A.; Aloni, S.; Philip Wong, H. S. Statistical Study on the Schottky Barrier Reduction of Tunneling Contacts to CVD Synthesized MoS<sub>2</sub>. *Nano Lett.* **2016**, *16* (1), 276–281.

(12) Liu, H.; Neal, A. T.; Ye, P. D. Channel Length Scaling of  $MoS_2$  MOSFETs. ACS Nano 2012, 6 (10), 8563–8569.

(13) Miao, J.; Zhang, S.; Cai, L.; Scherr, M.; Wang, C. Ultrashort Channel Length Black Phosphorus Field-Effect Transistors. *ACS Nano* **2015**, *9*, 9236–9243.

(14) Cao, W.; Liu, W.; Kang, J.; Banerjee, K. An Ultra-Short Channel Monolayer  $MoS_2$  FET Defined by the Curvature of a Thin Nanowire. *IEEE Electron Device Lett.* **2016**, 37 (11), 1497–1500.

(15) Liu, Y.; Guo, J.; Wu, Y.; Zhu, E.; Weiss, N. O.; He, Q.; Wu, H.; Cheng, H. C.; Xu, Y.; Shakir, I.; et al. Pushing the Performance Limit of Sub-100 Nm Molybdenum Disulfide Transistors. *Nano Lett.* **2016**, *16* (10), 6337–6342.

(16) Yoon, Y.; Ganapathi, K.; Salahuddin, S. How Good Can. Monolayer  $MoS_2$  Transistors Be? *Nano Lett.* **2011**, *11* (9), 3768–3773.

(17) Nourbakhsh, A.; Zubair, A.; Huang, S.; Ling, X.; Dresselhaus, M. S.; Kong, J.; De Gendt, S.; Palacios, T. 15-Nm Channel Length MoS2 FETs with Single- and Double-Gate Structures. In *Digest of Technical Papers - Symposium on VLSI Technology*; IEEE, 2015; pp T28–T29.

(18) Desai, S. B.; Madhvapathy, S. R.; Sachid, A. B.; Llinas, J. P.; Wang, Q.; Ahn, G. H.; Pitner, G.; Kim, M. J.; Bokor, J.; Hu, C.; et al. MoS<sub>2</sub> Transistors with 1-Nanometer Gate Lengths. *Science* **2016**, 354 (6308), 99–103.

(19) Chang, H.-Y.; Yang, S.; Lee, J.; Tao, L.; Hwang, W.-S.; Jena, D.; Lu, N.; Akinwande, D. High-Performance, Highly Bendable  $MoS_2$ Transistors with High-K Dielectrics for Flexible Low-Power Systems. *ACS Nano* **2013**, 7 (6), 5446–5452.

(20) Pu, J.; Yomogida, Y.; Liu, K.-K.; Li, L.-J.; Iwasa, Y.; Takenobu, T. Highly Flexible  $MoS_2$  Thin-Film Transistors with Ion Gel Dielectrics. *Nano Lett.* **2012**, *12* (8), 4013–4017.

(21) Lee, G.-H.; Yu, Y.-J.; Cui, X.; Petrone, N.; Lee, C.-H.; Choi, M. S.; Lee, D.-Y.; Lee, C.; Yoo, W. J.; Watanabe, K.; et al. Flexible and Transparent MoS<sub>2</sub> Field-Effect Transistors on Hexagonal Boron Nitride-Graphene Heterostructures. *ACS Nano* **2013**, 7 (9), 7931–7936.

(22) Jariwala, D.; Howell, S. L.; Chen, K. S.; Kang, J.; Sangwan, V. K.; Filippone, S. A.; Turrisi, R.; Marks, T. J.; Lauhon, L. J.; Hersam, M. C. Hybrid, Gate-Tunable, van Der Waals p-n Heterojunctions from Pentacene and MoS<sub>2</sub>. *Nano Lett.* **2016**, *16* (1), 497–503.

(23) Lee, C. H.; Lee, G. H.; van der Zande, A. M.; Chen, W.; Li, Y.; Han, M.; Cui, X.; Arefe, G.; Nuckolls, C.; Heinz, T. F.; et al. Atomically Thin P-n Junctions with van Der Waals Heterointerfaces. *Nat. Nanotechnol.* **2014**, *9* (9), 676–681.

(24) Georgiou, T.; Jalil, R.; Belle, B. D.; Britnell, L.; Gorbachev, R. V.; Morozov, S. V.; Kim, Y. J.; Gholinia, A.; Haigh, S. J.; Makarovsky, O.; et al. Vertical Field-Effect Transistor Based on Graphene-WS<sub>2</sub> Heterostructures for Flexible and Transparent Electronics. *Nat. Nanotechnol.* **2013**, *8* (2), 100–103.

(25) Novoselov, K. S.; Mishchenko, A.; Carvalho, A.; Castro Neto, A. H. 2D Materials and van Der Waals Heterostructures. *Science* **2016**, 353 (6298), aac9439.

(26) Withers, F.; Del Pozo-Zamudio, O.; Mishchenko, A.; Rooney, A. P.; Gholinia, A.; Watanabe, K.; Taniguchi, T.; Haigh, S. J.; Geim, A. K.; Tartakovskii, A. I.; et al. Light-Emitting Diodes by Band-Structure Engineering in van Der Waals Heterostructures. *Nat. Mater.* **2015**, *14* (3), 301–306.

(27) Liu, H.; Neal, A. T.; Ye, P. D. Channel Length Scaling of MoS<sub>2</sub> MOSFETs. ACS Nano **2012**, 6 (10), 8563–8569.

(28) Allain, A.; Kang, J.; Banerjee, K.; Kis, A. Electrical Contacts to Two-Dimensional Semiconductors. *Nat. Mater.* **2015**, *14* (12), 1195–1205.

(29) Schulman, D. S.; Arnold, A. J. Contact Engineering for 2D Materials and Devices. *Chem. Soc. Rev.* **2018**, *47*, 3037.

(30) Cheng, Z.; Price, K.; Franklin, A. D. Contacting and Gating 2-D Nanomaterials. *IEEE Trans. Electron Devices* **2018**, *65* (10), 4073–4083.

(31) Nasr, J. R.; Schulman, D. S.; Sebastian, A.; Horn, M. W.; Das, S. Mobility Deception in Nanoscale Transistors: An Untold Contact Story. *Adv. Mater.* **2019**, *31* (2), 1806020.

(32) Liu, W.; Kang, J.; Cao, W. High-Performance Few-Layer-MoS<sub>2</sub> Field-Effect-Transistor with Record Low Contact-Resistance. In *IEEE Technical Digest - International Electron Devices Meeting*; IEEE, 2013.

(33) Das, S.; Chen, H. Y.; Penumatcha, A. V.; Appenzeller, J. High Performance Multilayer  $MoS_2$  Transistors with Scandium Contacts. *Nano Lett.* **2013**, *13* (1), 100–105.

(34) Kappera, R.; Voiry, D.; Yalcin, S. E.; Branch, B.; Gupta, G.; Mohite, A. D.; Chhowalla, M. Phase-Engineered Low-Resistance Contacts for Ultrathin  $MoS_2$  Transistors. *Nat. Mater.* **2014**, *13* (12), 1128–1134.

(35) English, C. D.; Shine, G.; Dorgan, V. E.; Saraswat, K. C.; Pop, E. Improved Contacts to MoS<sub>2</sub> Transistors by Ultra-High Vacuum Metal Deposition. *Nano Lett.* **2016**, *16* (6), 3824–3830.

(36) International Technology Roadmap for Semiconductors 2.0: Executive Report. https://www.semiconductors.org/wp-content/uploads/2018/06/0\_2015-ITRS-2.0-Executive-Report-1.pdf.

(37) Auth, C.; Aliyarukunju, A.; Asoro, M.; Bergstrom, D.; Bhagwat, V.; Birdsall, J.; Bisnik, N.; Buehler, M.; Chikarmane, V.; Ding, G.; et al. A 10nm High Performance and Low-Power CMOS Technology Featuring 3rd Generation FinFET Transistors, Self-Aligned Quad Patterning, Contact over Active Gate and Cobalt Local Interconnects. In *IEEE International Electron Devices Meeting (IEDM)*; IEEE, 2017; pp 29.1.1–29.1.4.

(38) Razavieh, A.; Zeitzoff, P.; Brown, D. E.; Karve, G.; Nowak, E. J. Scaling Challenges of FinFET Architecture below 40nm Contacted Gate Pitch. In *Device Research Conference*; 2017.

(39) Wang, L.; Meric, I.; Huang, P. Y.; Gao, Q.; Gao, Y.; Tran, H.; Taniguchi, T.; Watanabe, K.; Campos, L. M.; Muller, D. a.; et al. One-Dimensional Electrical Contact to a Two-Dimensional Material. *Science* **2013**, *342* (6158), 614–617.

(40) Bollinger, M. V.; Lauritsen, J. V.; Jacobsen, K. W.; Nørskov, J. K.; Helveg, S.; Besenbacher, F. One-Dimensional Metallic Edge States in MoS<sub>2</sub>. *Phys. Rev. Lett.* **2001**, *87* (19), 196803.

(41) Guimarães, M. H. D.; Gao, H.; Han, Y.; Kang, K.; Xie, S.; Kim, C. J.; Muller, D. A.; Ralph, D. C.; Park, J. Atomically Thin Ohmic Edge Contacts between Two-Dimensional Materials. *ACS Nano* **2016**, *10* (6), 6392–6399.

(42) Zheng, J.; Yan, X.; Lu, Z.; Qiu, H.; Xu, G.; Zhou, X.; Wang, P.; Pan, X.; Liu, K.; Jiao, L. High-Mobility Multilayered  $MoS_2$  Flakes with Low Contact Resistance Grown by Chemical Vapor Deposition. *Adv. Mater.* **2017**, *29* (13), 1604540.

(43) Yoo, G.; Lee, S.; Yoo, B.; Han, C.; Kim, S.; Oh, M. S. Electrical Contact Analysis of Multilayer  $MOS_2$  Transistor With Molybdenum Source/Drain Electrodes. *IEEE Electron Device Lett.* **2015**, *36* (11), 1215–1218.

(44) Chai, Y.; Ionescu, R.; Su, S.; Lake, R.; Ozkan, M.; Ozkan, C. S.; From, I. Making One-Dimensional Electrical Contacts to Molybdenum Disulfide-Based Heterostructures through Plasma Etching. *Phys. Status Solidi A* **2016**, *1364* (5), 1358–1364.

(45) Cheng, Z.; Cardenas, J. A.; Mcguire, F.; Najmaei, S.; Franklin, A. D.; et al. Modifying the Ni-MoS<sub>2</sub> Contact Interface Using a Broad-Beam Ion Source. *IEEE Electron Device Lett.* **2016**, 37 (9), 1234–1237.

(46) Liu, Z.; Wu, Y.; Harteneck, B.; Olynick, D. Super-Selective Cryogenic Etching for Sub-10 Nm Features. *Nanotechnology* **2013**, 24 (1), 015305.

(47) Hoekstra, R. J.; Kushner, M. J.; Sukharev, V.; Schoenborn, P. Microtrenching Resulting from Specular Reflection during Chlorine

Etching of Silicon. J. Vac. Sci. Technol., B: Microelectron. Process. Phenom. 1998, 16 (4), 2102.

(48) Esashi, M.; Takinami, M.; Wakabayashi, Y.; Minami, K. High-Rate Directional Deep Dry Etching for Bulk Silicon Micromachining. J. Micromech. Microeng. **1995**, 5 (1), 5–10.

(49) Kang, J.; Matsumoto, Y.; Li, X.; Jiang, J.; Xie, X.; Kawamoto, K.; Kenmoku, M.; Chu, J. H.; Liu, W.; Mao, J.; et al. On-Chip Intercalated-Graphene Inductors for next-Generation Radio Frequency Electronics. *Nat. Electron.* **2018**, *1* (1), 46–51.

(50) Wang, C.; He, Q.; Halim, U.; Liu, Y.; Zhu, E.; Lin, Z.; Xiao, H.; Duan, X.; Feng, Z.; Cheng, R.; et al. Monolayer Atomic Crystal Molecular Superlattices. *Nature* **2018**, 555 (7695), 231–236.

(51) Xiong, F.; Wang, H.; Liu, X.; Sun, J.; Brongersma, M.; Pop, E.; Cui, Y. Li Intercalation in  $MoS_2$ : In Situ Observation of Its Dynamics and Tuning Optical and Electrical Properties. *Nano Lett.* **2015**, *15* (10), 6777–6784.

(52) Lai, S. L.; Johnson, D.; Westerman, R. Aspect Ratio Dependent Etching Lag Reduction in Deep Silicon Etch Processes. *J. Vac. Sci. Technol., A* **2006**, 24 (4), 1283–1288.

(53) Cheng, Z.; Abuzaid, H.; Yu, Y.; Zhang, F.; Li, Y.; Noyce, S. G.; Williams, N. X.; Lin, Y.-C.; Doherty, J. L.; Tao, C.; et al. Convergent Ion Beam Alteration of 2D Materials and Metal-2D Interfaces. 2D *Mater.* **2019**, *6* (3), 034005.

(54) Luo, B.; Liu, J.; Zhu, S. C.; Yi, L. Chromium Is Proposed as an Ideal Metal to Form Contacts with Monolayer MoS  $_2$  and WS  $_2$ . *Mater. Res. Express* **2015**, 2 (10), 106501.

(55) Neal, A. T.; Liu, H.; Gu, J. J.; Ye, P. D. Metal Contacts to  $MoS_2$ : A Two-Dimensional Semiconductor. In *Device Research Conference*; 2012.

(56) Alharbi, A.; Huang, Z.; Taniguchi, T.; Watanabe, K.; Shahrjerdi, D. Effect of Substrate Coupling on the Performance and Variability of Monolayer MoS  $_2$  Transistors. *IEEE Electron Device Lett.* **2019**, 40 (1), 135–138.

(57) Gurarslan, A.; Yu, Y.; Su, L.; Yu, Y.; Suarez, F.; Yao, S.; Zhu, Y.; Ozturk, M.; Zhang, Y.; Cao, L. Surface-Energy-Assisted Perfect Transfer of Centimeter-Scale Monolayer and Few-Layer MoS<sub>2</sub> Films onto Arbitrary Substrates. *ACS Nano* **2014**, *8* (11), 11522–11528.

(58) Zhang, X.; Han, J.; Plombon, J. J.; Sutton, A. P.; Srolovitz, D. J.; Boland, J. J. Nanocrystalline Copper Films Are Never Flat. *Science* **2017**, 357 (6349), 397–400.

(59) Mcclellan, C. J.; Yalon, E.; Smithe, K. K. H.; Suryavanshi, S. V.; Pop, E. Effective N-Type Doping of Monolayer MoS2 by  $AlO_X$ . In Device Research Conference; 2017.

(60) Lee, Y.-H.; Zhang, X.-Q.; Zhang, W.; Chang, M.-T.; Lin, C.-T.; Chang, K.-D.; Yu, Y.-C.; Wang, J. T.-W.; Chang, C.-S.; Li, L.-J.; et al. Synthesis of Large-Area  $MOS_2$  Atomic Layers with Chemical Vapor Deposition. *Adv. Mater.* **2012**, *24* (17), 2320–2325.

(61) Najmaei, S.; Liu, Z.; Zhou, W.; Zou, X.; Shi, G.; Lei, S.; Yakobson, B. I.; Idrobo, J. C.; Ajayan, P. M.; Lou, J. Vapour Phase Growth and Grain Boundary Structure of Molybdenum Disulphide Atomic Layers. *Nat. Mater.* **2013**, *12* (8), 754–759.

(62) Yu, Y.; Yu, Y.; Xu, C.; Cai, Y. Q.; Su, L.; Zhang, Y.; Zhang, Y. W.; Gundogdu, K.; Cao, L. Engineering Substrate Interactions for High Luminescence Efficiency of Transition-Metal Dichalcogenide Monolayers. *Adv. Funct. Mater.* **2016**, *26* (26), 4733–4739.