## Achieving low-voltage thin-film transistors using carbon nanotubes

Bumjung Kim, <sup>1</sup> Aaron Franklin, <sup>2</sup> Colin Nuckolls, <sup>1</sup> Wilfried Haensch, <sup>2</sup> and George S. Tulevski<sup>2,a)</sup>

<sup>1</sup>Department of Chemistry, Columbia University, New York, New York 10027, USA <sup>2</sup>IBM TJ Watson Research Center, 1101 Kitchawan Road, Yorktown Heights, New York 10598, USA

(Received 6 March 2014; accepted 15 July 2014; published online 12 August 2014)

The potential to perform at low voltages is a unique feature of carbon nanotube thin-film transistors (CNT-TFTs) when compared to more common TFT material options, such as amorphous Si or organic films. In this work, CNT-TFTs are fabricated using high-purity CNTs (verified electrically to be  $\sim$ 99% semiconducting) on an embedded gate device structure, which allows for scaling of the dielectric (equivalent oxide thickness  $\sim$  3 nm) and yields a high gate capacitance. The high gate capacitance, coupled with the high semiconducting purity, leads to devices with excellent low-voltage performance having an average subthreshold swing of  $\sim$ 200 mV/decade (low of  $\sim$ 90 mV/decade) and on/off current ratios of  $10^5$ . Testing hundreds of the CNT-TFTs on a chip at various channel lengths and widths provided a first look at the distribution of key performance metrics across a substrate. Favorable trade-offs between on-current and on/off current ratio were observed along with high field-effect mobility and narrow distributions in both the threshold voltage and subthreshold swing. The methods and results demonstrated here show that the low-voltage performance of CNT-TFTs is accessible for macroelectronic applications. © 2014 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4891335]

Thin-film transistors (TFTs) are ubiquitous structures used in the electronics industry for various macroelectronic applications including displays and sensors. Single-walled carbon nanotube (CNT) films are an excellent candidate for use as the channel material due to their superb electrical properties, mechanical flexibility, and compatibility with virtually any substrate. <sup>1–11</sup> Advances in solution processing, especially solution-based isolation of semiconducting CNTs, enables the fabrication of CNT-TFTs that outperform the industry standard, amorphous Si-TFTs. Such CNT-TFTs are fabricated using simple solution-based deposition techniques that are performed at room temperature and are compatible with virtually any substrate. <sup>12–18</sup>

Typical applications for macroelectronic devices and circuits (i.e., mobile and/or flexible displays, remote sensors, and circuits) will benefit from, and likely require, lowvoltage performance as power is generally limited in their configurations. Low-voltage operation requires that the TFT switches to the on-state over a small gate voltage range and, additionally, has good transport properties to provide sufficient drive current. The subthreshold swing (SS) of a device characterizes how much gate voltage is needed to switch from the off- to the on-state, and the channel mobility is a good figure of merit for how much current the transistor can drive. Both SS and mobility are improved by the use of CNT-TFTs compared to other available solutions. While single-CNT devices—where the CNT channel(s) spans the source and drain-can exhibit excellent low-voltage performance, 19-22 CNT-TFTs typically have much larger subthreshold swings ( $\sim$ 5–1 V/decade). Exceptions to this trend in the literature are devices fabricated with self-assembled monolayer (SAM) based dielectrics or ionic gel dielectrics where SS is reported as low as 130 mV/dec-ade<sup>25</sup>—the fundamental limit at room temperature is 60 mV/decade. Although these examples demonstrate the ability of low-voltage performance, a route using a more conventional and scalable device architecture has been elusive. Furthermore, it is important to demonstrate the reproducibility of such low-voltage CNT-TFTs by examining large distributions of devices across a substrate.

In this work, semiconducting CNTs are used as the channel material for TFTs with an embedded gate structure that enables exceptional performance at low operating voltage with average SS of 200 mV/decade (as low as 90 mV/ decade). The CNTs are sorted using column chromatography with a semiconducting purity greater than 99% verified both optically (UV-vis-NIR absorption spectroscopy) and with electrical measurements, as reported in an earlier work.<sup>17</sup> Raman spectroscopy on the CNT films confirms that additional defects are not introduced as a result of the solution processing. The embedded gate structure circumvents the difficult task of growing high quality dielectrics on carbon nanotubes;<sup>26</sup> allowing for employment of thin (10 nm) high quality HfO2 films as the dielectric as well as the ability to gate the devices individually. The thin dielectric (equivalent oxide thickness (EOT) of approximately 3 nm) yields a large gate capacitance, enabling the low SS. The use of high-purity semiconducting carbon nanotubes coupled with the embedded gate structure results in the exceptional low voltage performance in these CNT-TFTs.

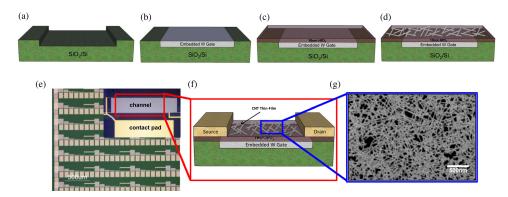

The device fabrication and layout are illustrated in Figure 1. The wafer consists of highly resistive silicon with 1  $\mu$ m of thermally grown SiO<sub>2</sub>. Gate trenches are patterned with photolithography followed by reactive ion etching (RIE) to produce 50 nm deep trenches in the SiO<sub>2</sub> (Figure 1(a)). The gate trench is then filled with tungsten metal and chemically mechanically polished (CMP) to planarize the

a) Author to whom correspondence should be addressed. Electronic mail: gstulevs@us.ibm.com

FIG. 1. Schematic of the process flow for embedded gate CNT-TFTs, including (a) the etching of the gate trench into the substrate, (b) filling and polishing of the W metal gate, (c) deposition via ALD of 10 nm of  $HfO_2$ , and the (d) modification of the gate oxide with poly-l-lysine followed by CNT deposition. The final device structure that includes the electrode deposition is illustrated in Figure 2(b). (e) An optical microscope image of an array of carbon nanotube thin-film transistors with varying lengths and widths and an (inset) image of a single CNT-TFT with a  $10 \mu m$  channel length and an  $80 \mu m$  channel width. (f) A schematic of a CNT-TFT illustrating the embedded gate structure, (g) a SEM image of a representative CNT film.

surface (Figure 1(b)). Atomic layer deposition (ALD) of 10 nm HfO<sub>2</sub> completes the gate stack (Figure 1(c)). The first three steps (Figures 1(a)–1(c)) were performed at wafer scale using a 200 mm CMOS line and then diced into individual chips prior to CNT deposition. Fabrication of this local-bottom gate (LBG) structure prior to CNT deposition obviates the need to grow a gate dielectric directly on the CNTs while allowing for individual gating of the devices. This is advantageous as growing high-quality, thin dielectrics on CNT films is extremely challenging due to a lack of reactive sites on the sp<sup>2</sup> bonded surface of the CNT. The HfO<sub>2</sub> surface is modified with poly-lysine (30% in water, Sigma-Aldrich), which aids in adsorption of the CNT network (Figure 1(d)).<sup>6</sup>

Large arrays of CNT-TFTs were fabricated with varying channel lengths and channel widths (as shown in Figure 1(e)) and designed to be compatible with a semi-automated probe station to allow for high-throughput characterization. After the CNT films are deposited, the channels are isolated via e-beam lithography to expose the areas of CNTs to be etched away outside of the channel. After etching of the unwanted CNTs in an oxygen plasma, the contacts (patterned via e-beam lithography) are metallized (Pd/Au). An estimated CNT density of  $\sim 8 \text{ CNTs}/\mu\text{m}^2$  is obtained after exposure to the semiconducting CNT solution for several hours as evidenced by the SEM image of Figure 1(g). The CNTs (ASP-100F, Hanwha Nanotech) are sorted (prior to device fabrication) by electronic type using column chromatography to isolate the semiconducting CNTs to purity levels >99%, as described in an earlier work. 17 Although the semiconducting fractions are screened using UV-vis-NIR absorption spectroscopy, the semiconducting purity is verified electrically by fabricating ~1000 individual CNT-FETs and counting how many are metallic or semiconducting.

Representative subthreshold and output curves of a CNT-TFT (channel length  $L_{\rm ch}=5~\mu m$ , and width  $W_{\rm ch}=80~\mu m$ ) are shown in Figures 2(a) and 2(b), respectively. The subthreshold curves are well-behaved at varying drain biases ( $V_{\rm ds}$ ) from -1~V down to -100~mV, with minimal curve shifting and a steady SS. The on/off current ration ( $I_{\rm ON}/I_{\rm OFF}$ ) is high ( $10^5$ ) and consistent at various  $V_{\rm ds}$ . Perhaps the most striking feature is that the SS is consistently low at varying drain bias with a value of  $\sim 200~mV/decade$ . This low SS coupled with the high  $I_{\rm ON}/I_{\rm OFF}$  and low threshold voltage (0.8~V) make

these devices promising for low-voltage applications. The output curves (Figure 2(b)) show strong current saturation at  $V_{DS} < 1 \, V$ , with the linear behavior at low  $V_{ds}$  indicating Ohmic-like contacts.

As the channel lengths are several times larger than the average length of the CNTs ( $\sim$ 500 nm), the devices operate in a percolation regime where the carriers transport across many CNTs to traverse the channel from source to drain. A

FIG. 2. (a)  $I_{ds}$  vs.  $V_g$  curve for a CNT-TFT with a channel length of  $5\,\mu m$  and a channel width of  $80\,\mu m$  at various drain-source biases. The dotted line indicates a subthreshold swing of  $200\,mV/dec$ . (b)  $I_{ds}$  vs.  $V_{ds}$  curve for the same CNT-TFT at various gate biases. The curves show clear saturation behavior and Ohmic-like contacts.

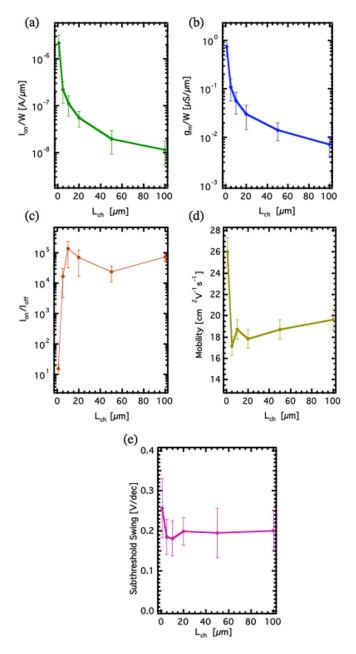

series of device performance parameters as a function of channel length are shown in Figures 3(a)–3(e). As expected, the on–current (Figure 3(a)) and peak transconductance ( $g_m$  in Figure 3(b)) both decrease with increasing channel length. This is due to the increasing number of CNT-CNT junctions present as  $L_{ch}$  is increased. Conversely, the  $I_{on}/I_{off}$  ratio increases dramatically with channel length from a value of 10 at  $L_{ch}$  of  $1~\mu m$  to where it saturates at  $\sim 10^5$ . The slope of this increase is very sharp and indicative of the high level of purity of the semiconducting samples. The saturation of  $I_{ON}/I_{OFF}$  at  $\sim 10^5$  is typical of CNTs in the larger diameter range, where the bandgaps are smaller, and is not due to the presence of metallic pathways.<sup>24</sup>

The field-effect mobility was calculated using gate capacitance values obtained through high-frequency

FIG. 3. Channel length dependence of the CNT-TFTs (channel width =  $80\,\mu\text{m}$ ) on (a)  $I_{\text{on}}/W$  [A/ $\mu\text{m}$ ], (b)  $g_{\text{m}}/W$  [ $\mu\text{S}/\mu\text{m}$ ], (c)  $I_{\text{on}}/I_{\text{off}}$ , (d) mobility, and (e) subthreshold swing [mV/decade]. All the parameters presented here behave as expected from a device operating in the percolation regime.

electrical measurements. This allows for a precise calculation of the capacitance, and thus, the field-effect mobility. Since the source/drain contacts overlap the gate dielectric, the measured capacitance was corrected to remove the parasitic capacitance between the gate metal and source/drain contacts. Because the source/drain contacts are narrow (300 nm) with respect to the device area, the correction is relatively small ( $\sim$ 15%). The mobility is plotted versus channel length in Figure 3(d) and decreases slightly ( $\sim$ 25%) as the channel length increases before saturating at  $\sim 18 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ . The elevated mobility at small channel lengths is due to the presence of metallic pathways in the film at channel lengths of  $1 \, \mu m$ . The subthreshold swing decreases slightly at  $L_{ch}$  from  $1 \,\mu \text{m}$  to  $5 \,\mu \text{m}$  before saturating at  $\sim 200 \,\text{mV/decade}$ . This behavior is expected as the SS typically increases if the I<sub>ON</sub>/I<sub>OFF</sub> is small owing to a clipping of the off-state by the increased dominance of metallic CNTs. It is also worth noting that the spread in values for SS at channel lengths of 5  $\mu$ m and above is small with a range of 90 mV/decade–320 mV/decade.

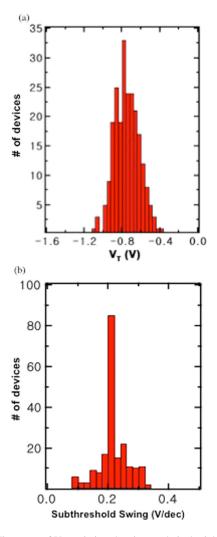

The device layout was designed such that several hundred devices could be measured using a semi-automated probe station to obtain statistics on device-to-device variability. Figures 4(a) and 4(b) are histograms of the number of devices versus threshold voltage  $(V_T)$  and SS, respectively.

FIG. 4. (a) Histogram of  $V_T$  variation showing a relatively tight distribution and (b) histogram of the subthreshold swing yielding a tight distribution with a remarkably low value for devices of such large dimensions.

The  $V_T$  was centered at -0.8 V with relatively low variation (ranging from -0.4 V to -1.2 V). The SS displayed similar consistency and was centered at  $\sim 200$  mV/dec.

Subthreshold swing can be expressed using the following equation: 11,27

$$SS = \left(\frac{k_B T}{e}\right) \ln(10) \left(1 + \frac{C_{IT}}{C_i}\right),\,$$

where the value of SS above the room temperature limit of 60 mV/decade is determined by  $C_{IT}/C_i-C_{IT}$  is the capacitance resulting from interface traps,  $C_i$  is the gate capacitance,  $k_B$ is the Boltzmann constant, T is temperature, and e is the elementary charge of an electron. If  $C_{IT}$  is very small compared to  $C_i$ , then the SS approaches the limit of  $60 \,\mathrm{mV/decade}$  at room temperature. The  $C_{IT}$  is not greatly reduced in these devices versus previous literature results as similar dielectrics and interfacial organic layers are used. The dramatically reduced SS is more likely due to an increase in Ci as our dielectric thickness is greatly reduced and acts to screen out the effects of  $C_{IT}$ . The increased gate capacitance is enabled by the embedded gate geometry allow from extremely scaled dielectrics, and thus, high gate capacitance. This explanation is also consistent with the low SS values obtained from the devices with a monolayer dielectric and an ionic dielectric, both of which have high  $C_i$ . 5,25,28 These results demonstrate that one critical feature of low-voltage operation in CNT-TFTs is a high gate capacitance.

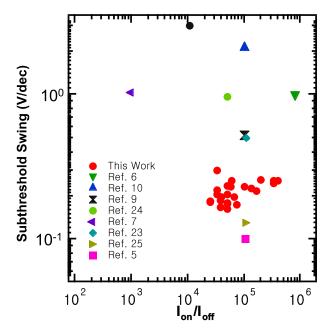

The exceptional low-voltage performance of these embedded gate CNT-TFTs is highlighted in the scatter plot (Figure 5) of SS versus  $I_{\rm ON}/I_{\rm OFF}$ . The goal is to push data points toward the bottom right of the plot, where the SS is low and the  $I_{\rm ON}/I_{\rm OFF}$  is high. The red points were taken from devices with varying channel lengths (5–100  $\mu$ m) at a fixed channel width of 80  $\mu$ m. Despite the varying  $I_{\rm ON}/I_{\rm OFF}$  (due to differences in channel length), the subthreshold swings are consistently small ( $\sim$ 200 mV/dec) with high  $I_{\rm ON}/I_{\rm OFF}$

FIG. 5. (a) Plot of subthreshold swing versus  $I_{ON}/I_{OFF}$ . The data in red is from this work, while other data were extracted from I-V curves in literature references as noted.

obtained in longer (>5  $\mu$ m) channel length devices. On the same plot, several representative CNT-TFT devices from key literature examples are also plotted. Although they have similar  $I_{ON}/I_{OFF}$  ratios, the subthreshold swings (extracted from the figures) are  $2\times-10\times$  greater at the same  $I_{ON}/I_{OFF}$  ratios. This highlights the exceptional low voltage performance attained by coupling high-purity semiconducting CNTs with an embedded gate structure (which allows for thin EOT).

Exceptional low-voltage performance is demonstrated with CNT-TFTs that employ highly enriched semiconducting CNT solutions and embedded metal gate device geometry. Since the devices operate in the percolation regime, there are expected trade-offs between on-current and  $I_{\rm ON}/I_{\rm OFF}$  ratio. The device performance metrics (i.e., mobility,  $I_{\rm ON}/I_{\rm OFF}$ ,  $g_{\rm M}$  and SS) are competitive with, and in some cases better than, conventional thin-film technologies. The key to obtain low-voltage performance is dramatically increasing the gate capacitance to screen the capacitance generated by interfacial charge traps in thin film channel devices. These structures are ideally suited for macroelectronics that would benefit from operating at lower voltages to save on active power.

The authors acknowledge James Bucchigiano for performing the electron beam lithography, IBM's Materials Research Laboratory for the wafer fabrication and Qing Cao, Jerry Tersoff, and Shu-jen Han for helpful discussions.

<sup>1</sup>E. S. Snow, J. P. Novak, P. M. Campbell, and D. Park, Appl. Phys. Lett. **82**, 2145 (2003).

<sup>2</sup>E. Artukovic, M. Kaempgen, D. S. Hecht, S. Roth, and G. Grüner, Nano Lett. 5, 757 (2005).

<sup>3</sup>C. Wang, J. Zhang, K. Ryu, A. Badmaev, L. de Arco, and C. Zhou, Nano Lett. **9**, 4285 (2009).

<sup>4</sup>S. J. Kang, C. Kocabas, T. Ozel, M. Shim, N. Pimparkar, M. A. Alam, S. V. Rotkin, and J. A. Rogers, Nat. Nanotechnol. **2**, 230 (2007).

<sup>5</sup>V. K. Sangwan, R. P. Ortiz, J. M. P. Alaboson, J. D. Emery, M. J. Bedzyk, L. J. Lauhon, T. J. Marks, and M. C. Hersam, ACS Nano 6, 7480 (2012).

<sup>6</sup>T. Takahashi, K. Takei, A. G. Gillies, R. S. Fearing, and A. Javey, Nano Lett. 11, 5408 (2011).

<sup>7</sup>C. Wang, J.-C. Chien, K. Takei, T. Takahashi, J. Nah, A. M. Niknejad, and A. Javey, Nano Lett. 12, 1527 (2012).

<sup>8</sup>L. S. Liyanage, H. Lee, N. Patil, S. Park, S. Mitra, Z. Bao, and H.-S. P. Wong, ACS Nano 6, 451 (2012).

<sup>9</sup>M. Engel, J. Small, M. Steiner, M. Freitag, A. Green, M. Hersam, and P. Avouris, ACS Nano 2, 2445 (2008).

<sup>10</sup>C. Wang, J. Zhang, and C. Zhou, ACS Nano 4, 7123 (2010).

<sup>11</sup>S. Kumar, N. Pimparkar, J. Y. Murthy, and M. A. Alam, Appl. Phys. Lett. 88, 123505 (2006).

<sup>12</sup>M. S. Arnold, A. A. Green, J. F. Hulvat, S. I. Stupp, and M. C. Hersam, Nat. Nanotechnol. 1, 60 (2006).

<sup>13</sup>M. Zheng, A. Jagota, M. S. Strano, A. P. Santos, P. Barone, S. G. Chou, B. A. Diner, M. S. Dresselhaus, R. S. McLean, G. B. Onoa, G. G. Samsonidze, E. D. Semke, M. Usrey, and D. J. Walls, Science 302, 1545 (2003).

<sup>14</sup>H. W. Lee, Y. Yoon, S. Park, J. H. Oh, S. Hong, L. S. Liyanage, H. Wang, S. Morishita, N. Patil, Y. J. Park, J. J. Park, A. Spakowitz, G. Galli, F. Gygi, P. H. S. Wong, J. B. H. Tok, J. M. Kim, and Z. Bao, Nat. Commun. 2, 541 (2011).

<sup>15</sup>S. Park, H. W. Lee, H. Wang, S. Selvarasah, M. R. Dokmeci, Y. J. Park, S. N. Cha, J. M. Kim, and Z. Bao, ACS Nano 6, 2487 (2012).

<sup>16</sup>K. Moshammer, F. Hennrich, and M. M. Kappes, Nano Res. 2, 599 (2009).

S. Tulevski, A. D. Franklin, and A. Afzali, ACS Nano 7, 2971 (2013).

Khripin, J. A. Fagan, and M. Zheng, J. Am. Chem. Soc. 135, 6822

<sup>19</sup>A. D. Franklin and Z. Chen, Nat. Nanotechnol. **5**, 858 (2010).

<sup>20</sup>A. D. Franklin, M. Luisier, S.-J. Han, G. Tulevski, C. M. Breslin, L. Gignac, M. S. Lundstrom, and W. Haensch, Nano Lett. 12, 758 (2012).

- <sup>21</sup>A. Javey, J. Guo, D. B. Farmer, Q. Wang, E. Yenilmez, R. G. Gordon, M. Lundstrom, and H. Dai, Nano Lett. 4, 1319 (2004).

- <sup>22</sup>P. Avouris, Phys. Today **62**(1), 34 (2009).

- <sup>23</sup>S. Y. Lee, S. W. Lee, S. M. Kim, W. J. Yu, Y. W. Jo, and Y. H. Lee, ACS Nano 5, 2369 (2011).

- <sup>24</sup>Y. Asada, F. Nihey, S. Ohmori, H. Shinohara, and T. Saito, Adv. Mater. (Weinheim, Ger) 23, 4631 (2011).

- <sup>25</sup>M. Ha, Y. Xia, A. A. Green, W. Zhang, M. J. Renn, C. H. Kim, M. C. Hersam, and C. D. Frisbie, ACS Nano 4, 4388 (2010).

- <sup>26</sup>D. B. Farmer and R. G. Gordon, Nano Lett. **6**, 699 (2006).

- <sup>27</sup>Q. Cao, M. G. Xia, M. Shim, and J. A. Rogers, Adv. Funct. Mater. 16, 2355 (2006).

- <sup>28</sup>J. H. Cho, J. Lee, Y. Xia, B. Kim, Y. He, M. J. Renn, T. P. Lodge, and C. D. Frisbie, Nat. Mater. 7, 900 (2008).