# Unanticipated Polarity Shift in Edge-Contacted Tungsten-Based 2D Transition Metal Dichalcogenide Transistors

Hattan Abuzaid<sup>®</sup>, Student Member, IEEE, Zhihui Cheng, Guoqing Li, Linyou Cao, and Aaron D. Franklin<sup>®</sup>, Senior Member, IEEE

Abstract—Creating metal edge contacts in transition metal dichalcogenide (TMD) transistors is a promising path to advance transistor miniaturization for future technology nodes. Current experimental demonstrations nearly exclusively focus on MoS<sub>2</sub> as the channel material. Here, we create edge-contacted WSe2 and WS<sub>2</sub> transistors using a convergent Ar<sup>+</sup> ion beam source integrated within an e-beam evaporator chamber for in-situ processing. An unanticipated polarity shift was observed compared to top-contact behavior for Ti-WS<sub>2</sub> devices, which displayed p-type conduction. Meanwhile, three distinct metal contact materials yielded comparable p-branch-dominant performance on WSe<sub>2</sub>. Transmission electron microscope (TEM) imaging with energy dispersive spectroscopy (EDS) analysis indicated the existence of a residual layer of W (and chalcogen atoms to a lesser extent) beneath the metal contacts, even though the substrate was over-etched. The images presented a physically pure edge interface. This intriguing etching effect could carry significant implications for the design of tungsten-based, edge-contacted TMD transistors.

Index Terms— Edge contacts, transition metal dichalcogenide (TMD), field-effect transistor (FET), carrier injection, ion beam.

#### I. Introduction

THE experimental demonstration of air-stable monolayers of graphene in 2004 generated overwhelming interest in 2D materials [1]. One subfamily of the 2D crystals, the transition metal dichalcogenides (TMD), emerged as a strong candidate for atomically thin-body field-effect transistors (FETs) [2]. Despite showing excellent performance, 2D FETs as they stand cannot compete with state-of-the-art silicon

Manuscript received August 5, 2021; accepted August 17, 2021. Date of publication August 20, 2021; date of current version September 27, 2021. This work was supported by the National Science Foundation under Grant ECCS 1915814. The review of this letter was arranged by Editor G. Han. (Corresponding author: Aaron D. Franklin.)

Hattan Abuzaid and Aaron D. Franklin are with the Department of Electrical and Computer Engineering, Duke University, Durham, NC 27708 USA (e-mail: aaron.franklin@duke.edu).

Zhihui Cheng was with the Department of Electrical and Computer Engineering, Duke University, Durham, NC 27708 USA. He is now with the Nanoscale Device Characterization Division, National Institute of Standards and Technology, Gaithersburg, MD 20899 USA and also with the Department of Electrical and Computer Engineering, Purdue University, West Lafayette, IN 47907 USA.

Guoqing Li and Linyou Cao are with the Department of Materials Science and Engineering, North Carolina State University, Raleigh, NC 27606 USA.

Digital Object Identifier 10.1109/LED.2021.3106286

FinFETs. One of the main disadvantages is the high contact resistance ( $R_{\rm C}$ ) that forms at the interface between the metal contact and the TMD surface [3]. Injected carriers in 2D FETs must tunnel through a physical vdW gap [4] in addition to a substantial Schottky barrier that often arises from strong Fermi level pinning-like behavior [5], [6].

Researchers have reported several techniques to address the contact resistance challenge. The suggested solutions include using semi-metallic metal contact [7], [8], adding an interlayer [8], post-process annealing [9], doping [10], [11], surface phase engineering [12], and ion bombardment [13], [14]. Another, less-investigated path towards improving metal-2D contacts involves changing the contact configuration from a top contact to an edge contact. While TMD surfaces are generally inert, their sides are reactive, which should translate to covalent bonds forming at the metal-TMD interface and a vanishing vdW tunneling gap [15]. More importantly, edge contacts offer maximum device scalability [16] and 3D integration compatibility.

There is an expansive library of semiconducting TMDs that have not been examined yet for edge-contacted transistors [17]; in fact, experimental reports to date are almost exclusively focused on MoS<sub>2</sub> [16], [18]–[23] with the exception of the work by Chu *et al.* [24] and the WS<sub>2</sub> 300 mm pilot line integration work at imec, which reported an unanticipated and unexplained p-type polarity shift [25], [26]. In this study, we report edge-contacted transistors made from the less-explored WSe<sub>2</sub> and WS<sub>2</sub> using a facile fabrication strategy and explore the underlying cause of the unanticipated polarity shift. The fabrication setup yields clean edge contacts by utilizing an *in-situ* ion beam source embedded in a high-vacuum evaporation chamber [16].

#### II. DEVICE FABRICATION

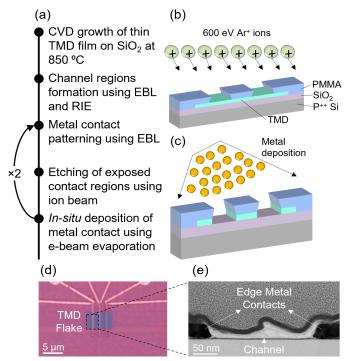

The major processing steps in creating the edge-contacted transistors in this study are shown in Fig. 1(a). WSe $_2$  and WS $_2$  films were grown directly using chemical vapor deposition (CVD) on Si p $^{++}$  substrates with 300 nm SiO $_2$  at 850 °C. Subsequently, the chips were coated with polymethyl methacrylate (PMMA) resist and alignment marks were patterned using electron beam lithography (EBL). 20 nm Ti/20 nm Au were deposited to form the alignments marks. After that, suitable TMD regions were located to pattern as the transistor channels. The as-grown film covers the entire

0741-3106 © 2021 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

Fig. 1. Fabrication of edge contacts on WS<sub>2</sub> and WSe<sub>2</sub> using *in-situ* Ar<sup>+</sup> ion beam. (a) Major processing steps (steps 3-5 are repeated two more times to yield three distinct contact materials on the same channel). (b) Schematic of *in-situ* ion beam etching step to expose TMD edge. (c) Schematic of e-beam evaporation step immediately after ion beam irradiation to create source and drain contacts. (d) Optical image of a finished device set. (e) Cross-sectional TEM image of one device within a device set. RIE: reactive ion etching.

substrate, so EBL patterning was used to form resist bars over the channels followed by a reactive ion etch (RIE) to cleanly remove the TMD from essentially everywhere but the channel regions. For the RIE, CF<sub>4</sub> gas was utilized to etch the area around the hardened PMMA bar. Following lift-off, a single set of contact leads was patterned on each channel region. Afterwards, the sample was loaded in the custom evaporator tool and the convergent ion source was operated at a beam energy of 600 eV (Fig. 1(b)) [14]. The recipe was started after the pressure in the chamber reached around  $10^{-7}$  torr to ensure minimal contamination of the TMD etched edges. Immediately after the 15s etch, 15 - 25 nm of metal was deposited as the contact lead (Fig. 1(c)). These steps were repeated two more times to create two more sets of different metal leads on the same channel region. The three metals that were selected for WS<sub>2</sub> are Ag, Ti and Ni, while the ones for WSe<sub>2</sub> are Pd, Ti and Ni. The metals were selected based on their distinct work functions, observed reactivity to TMDs [27], and their performance in top-contacted devices. Fig. 1(d) depicts a completed device set with three different metal contacts on the same TMD film whereas Fig. 1(e) shows a cross-sectional transmission electron microscope (TEM) image of one device within that set.

For electrical testing, the devices were modulated by applying a back-gate voltage to the probe station stage (chuck), which is connected to the doped silicon substrate and gates the channel through the 300 nm SiO<sub>2</sub> gate oxide. All WS<sub>2</sub> transistors had channel length  $L_{\rm CH}=200$  nm and channel width  $W_{\rm CH}=3~\mu{\rm m}$  while the WSe<sub>2</sub> devices had  $L_{\rm CH}=200$  nm and  $W_{\rm CH}=4~\mu{\rm m}$ .

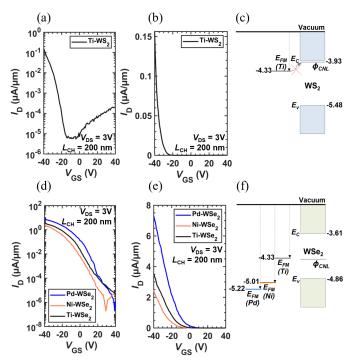

Fig. 2. Characteristics of the edge-contacted WS<sub>2</sub> and WSe<sub>2</sub> FETs. (a-b) Subthreshold and transfer I-V characteristics of trilayer edge-contacted Ti-WS<sub>2</sub> device showing unanticipated p-type conduction. (c) Conceptual energy band alignment based on clean metal work functions of the Ti-WS<sub>2</sub> system (energies are in eV). (d-e) Subthreshold and transfer I-V characteristics of three distinct edge-contact metals on the same bilayer WSe<sub>2</sub> channel exhibiting similar performance. (f) Conceptual energy band alignment based on clean metal work functions of the metal-WSe<sub>2</sub> systems. All measurements were done at room temperature.  $\phi_{\text{CNI}}$ : charge neutrality level.  $E_{\text{FM}}$ : metal Fermi level.

### III. RESULTS AND DISCUSSION

Ti-WS<sub>2</sub> device surprisingly exhibited p-type conduction, as seen in the transfer characteristics in Fig. 2(a-b). This is unexpected considering the persistence of top-contacted WS2 to form n-type or ambipolar transistors [28], [29], along with the Ti work function having close conceptual alignment with the charge neutrality level of WS<sub>2</sub>, which is near the conduction band minimum (Fig. 2(c)). This interesting behavior was previously reported by researchers at imec as part of integrating WS<sub>2</sub> transistors in a 300 mm pilot line [25], [26]. The researchers contacted the edges of an embedded, atomic layer deposition (ALD) grown WS<sub>2</sub> channel using Ti/TiN side contacts [25]; however, they did not explore the underlying causes of the unexpected polarity shift. In our device, the sizable bandgap of WS<sub>2</sub> ( $\sim$ 1.18 eV for a trilayer [30]) yielded a reasonable  $I_{ON}/I_{OFF}$ of  $\sim 10^4$ . The on-current of 0.16  $\mu$ A/ $\mu$ m is modest and within the same order of magnitude as some edge-contacted MoS<sub>2</sub> demonstrations [16], [21], [22]. Unfortunately, the WS<sub>2</sub> sample had poor functional device yield of only 2-3 % with the analyzed Ti-WS<sub>2</sub> transistor in Fig. 2(a-c) exhibiting the top performance. This difference in yield compared to the imec work is attributed to our WS<sub>2</sub> being fully exposed to ambient conditions (i.e., no capping layers) whereas the imec devices had fully embedded WS2 that was less prone to deleterious reactivity effects and mechanical deformation of the edge structure at the metal-semiconductor junction.

In addition to the WS<sub>2</sub> devices, three distinct metal contacts (Pd, Ti, and Ni) were explored on the same WSe<sub>2</sub> channel to eliminate performance differences due to film spatial variations. All three metal contacts performed quite similarly, with Pd having a slight edge with the best on-state, as seen in Fig. 2(d-e), including an on-current of 7.3  $\mu$ A/ $\mu$ m. This oncurrent is comparable with some of the best values reported for edge-contacted MoS<sub>2</sub> [16], [21], [22], which is encouraging considering MoS<sub>2</sub> top-contacted FETs outperform their WSe<sub>2</sub> counterparts by a large margin. Moreover, the three WSe2 devices had an impressive  $I_{ON}/I_{OFF}$  of  $\sim 10^6$ . The p-type behavior from the three metals is not as surprising as it was for Ti-WS2 and it conforms with reported literature for topcontacted devices (conceptual band alignment illustrated in Fig.2(f)). The Ti-WSe<sub>2</sub> transistor did perform unexpectedly better than the Ni-WSe<sub>2</sub> device if the simple band alignment picture is used for comparison.

While the results we present for edge-contacted  $WS_2$  and  $WSe_2$  transistors are encouraging, top-contacted devices from the literature still outperform them [7], [31]. Top contacts have been heavily investigated for many years and have gone through numerous improvements and advancements. On the other hand, edge contacts (particularly to W-based TMDs) have not reached the same level of maturity to justify a direct comparison. Extensive research is still required to demystify the carrier injection behavior at edge interfaces and optimize the fabrication approach. Theoretical studies have suggested better performance from edge contacts than their top contact counterpart [18], but more extensive experimental studies are needed to validate this projection.

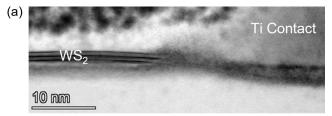

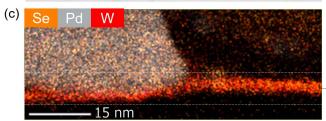

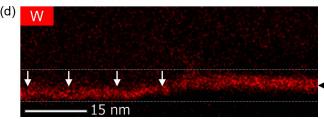

Cross-sectional TEM imaging was conducted on the electrically characterized devices to confirm edge contact formation as depicted in Fig. 3(a-b). The TEM images, along with energy dispersive spectroscopy (EDS) analysis, revealed intriguing insight beyond edge contact verification. Fig. 3(c-d) reveals the existence of a W layer beneath the metal contact, which originates from the etched WSe<sub>2</sub> in spite of substrate overetching. The lack of this effect in edge-contacted MoS2 transistors could be due to W being twice as heavy as Mo, leading it to settle into the etched substrate rather than be fully evacuated from the contact region. Se (or S for WS<sub>2</sub>) was also present below the contact (Fig. 3(c)), albeit with a less-prominent signal than W. It is important to note that WS<sub>2</sub> devices, such as the one in Fig. 3(a), also exhibited the same W-residual effect. These findings can explain why three metal contact materials displayed similar I-V curves for WSe<sub>2</sub> as the transistor effectively utilized W, or a compound therefrom, as the edge-contact material. The device yield discrepancy between WS2 and WSe2 samples could also be explained by the high resistivity of residual S beneath WS2 contacts compared to the more conductive Se below WSe<sub>2</sub> contacts.

Based on the EDS data, the most likely explanation for the p-branch-dominant behavior of the Ti-WS<sub>2</sub> device is that a composite metal was formed and serves as the contact rather than pure Ti or W. This is not to suggest that it is simply metal work function modification from such a metal compound that is responsible for the polarity shift; modification of the work function would be only one factor along with the change

Fig. 3. Cross-sectional TEM images of the fabricated edge-contact devices. (a) TEM image of Ti-WS<sub>2</sub> device confirming edge contact formation on the trilayer WS<sub>2</sub>. (b) TEM image of Pd-WSe<sub>2</sub> device confirming edge contact formation on the bilayer WSe<sub>2</sub>. (c) EDS elemental map of Pd-WSe<sub>2</sub> device only highlighting Pd, Se and W. (d) EDS elemental map of image in (c) only highlighting W, showing significant W content beneath the contact region despite over-etching of the substrate.

in bonding structure, pinning behavior, and various carrier transport dynamics. Other potential factors contributing to this phenomenon are the apparent damage to the WS<sub>2</sub> channel near the metal contact (Fig. 3(a-b)), though the devices from Ref. [25] did not appear to present this interfacial damage and still exhibited unexpected p-type behavior. Ultimately, this observation of residual W and chalcogen in edge contacts makes it possible for further, more focused analyses to be carried out towards understanding these distinct interfaces.

## IV. CONCLUSION

We presented the creation of edge-contacted transistors on less-investigated TMDs, namely, WSe<sub>2</sub> and WS<sub>2</sub>. A convergent Ar<sup>+</sup> ion beam source that is embedded in a custom, high-vacuum e-beam evaporation chamber is utilized for *insitu* processing. The Ti-WS<sub>2</sub> device exhibited unanticipated p-type conduction whereas three metals (Pd, Ni and Ti) performed similarly on WSe<sub>2</sub>. TEM imaging and EDS analysis unraveled some of the mystery by indicating the presence of a residual W-Se (for WSe<sub>2</sub> FETs) or W-S (for WS<sub>2</sub> FETs) layer beneath the metal contacts despite the over-etched substrate. Consideration of this unique etching effect could be essential for tungsten-based, edge-contacted TMD transistors.

#### REFERENCES

- K. S. Novoselov, A. K. Geim, S. V. Morozov, D. Jiang, Y. Zhang, S. V. Dubonos, I. V. Grigorieva, and A. A. Firsov, "Electric field effect in atomically thin carbon films," *Science*, vol. 306, no. 5696, pp. 666–669, 2004, doi: 10.1126/science.1102896.

- [2] Y. Liu, X. Duan, H.-J. Shin, S. Park, Y. Huang, and X. Duan, "Promises and prospects of two-dimensional transistors," *Nature*, vol. 591, no. 7848, pp. 43–53, Mar. 2021, doi: 10.1038/s41586-021-03339-z.

- [3] Z. Cheng, K. Price, and A. D. Franklin, "Contacting and gating 2-D nanomaterials," *IEEE Trans. Electron Devices*, vol. 65, no. 10, pp. 4073–4083, Oct. 2018, doi: 10.1109/TED.2018.2865642.

- [4] D. S. Schulman, A. J. Arnold, and S. Das, "Contact engineering for 2D materials and devices," *Chem. Soc. Rev.*, vol. 47, no. 9, pp. 3037–3058, 2018, doi: 10.1039/C7CS00828G.

- [5] C. M. Smyth, R. Addou, C. L. Hinkle, and R. M. Wallace, "Origins of Fermi-level pinning between molybdenum dichalcogenides (MoSe<sub>2</sub>, MoTe<sub>2</sub>) and bulk metal contacts: Interface chemistry and band alignment," *J. Phys. Chem. C*, vol. 123, no. 39, pp. 23919–23930, Aug. 2019, doi: 10.1021/acs.jpcc.9b04355.

- [6] C. M. Smyth, R. Addou, C. L. Hinkle, and R. M. Wallace, "Origins of Fermi level pinning between tungsten dichalcogenides (WS<sub>2</sub>, WTe<sub>2</sub>) and bulk metal contacts: Interface chemistry and band alignment," *J. Phys. Chem. C*, vol. 124, no. 27, pp. 14550–14563, Jun. 2020, doi: 10.1021/acs.jpcc.0c01646.

- [7] P.-C. Shen, C. Su, Y. Lin, A.-S. Chou, C.-C. Cheng, J.-H. Park, M.-H. Chiu, A.-Y. Lu, H.-L. Tang, M. M. Tavakoli, G. Pitner, X. Ji, Z. Cai, N. Mao, J. Wang, V. Tung, J. Li, J. Bokor, A. Zettl, C.-I. Wu, T. Palacios, L.-J. Li, and J. Kong, "Ultralow contact resistance between semimetal and monolayer semiconductors," *Nature*, vol. 593, no. 7858, pp. 211–217, May 2021, doi: 10.1038/s41586-021-03472-9.

- [8] K. Andrews, A. Bowman, U. Rijal, P.-Y. Chen, and Z. Zhou, "Improved contacts and device performance in MoS<sub>2</sub> transistors using a 2D semiconductor interlayer," ACS Nano, vol. 14, no. 5, pp. 6232–6241, Apr. 2020, doi: 10.1021/acsnano.0c02303.

- [9] M. Abraham and S. E. Mohney, "Annealed Ag contacts to MoS<sub>2</sub> field-effect transistors," *J. Appl. Phys.*, vol. 122, no. 11, Sep. 2017, Art. no. 115306, doi: 10.1063/1.4991961.

- [10] H. Huang, L. Wang, Y. Lv, X. Liu, X. Zhao, L. Liao, Z. Fan, and X. Zou, "High-performance WSe<sub>2</sub> n-type field-effect transistors enabled by InOx damage-free doping," *IEEE Electron Device Lett.*, vol. 42, no. 7, pp. 1081–1084, Jul. 2021, doi: 10.1109/LED.2021.3082140.

- [11] C.-S. Pang, T. Y. Hung, A. Khosravi, R. Addou, R. M. Wallace, and Z. Chen, "Doping-induced Schottky-barrier realignment for unipolar and high hole current WSe<sub>2</sub> devices with > 10<sup>8</sup> on/off ratio," *IEEE Electron Device Lett.*, vol. 41, no. 7, pp. 1122–1125, Jul. 2020, doi: 10.1109/LED.2020.2999258.

- [12] R. Kappera, D. Voiry, S. E. Yalcin, B. Branch, G. Gupta, A. D. Mohite, and M. Chhowalla, "Phase-engineered low-resistance contacts for ultrathin MoS<sub>2</sub> transistors," *Nature Mater.*, vol. 13, no. 12, pp. 1128–1134, Aug. 2014, doi: 10.1038/nmat4080.

- [13] J. Zhu, Z. Wang, H. Yu, N. Li, J. Zhang, J. Meng, M. Liao, J. Zhao, X. Lu, L. Du, R. Yang, D. Shi, Y. Jiang, and G. Zhang, "Argon plasma induced phase transition in monolayer MoS<sub>2</sub>," *J. Amer. Chem. Soc.*, vol. 139, no. 30, pp. 10216–10219, Jul. 2017, doi: 10.1021/jacs.7b05765.

- [14] Z. Cheng, H. Abuzaid, Y. Yu, F. Zhang, Y. Li, S. G. Noyce, N. X. Williams, Y.-C. Lin, J. L. Doherty, C. Tao, L. Cao, and A. D. Franklin, "Convergent ion beam alteration of 2D materials and metal-2D interfaces," 2D Mater., vol. 6, no. 3, Jun. 2019, Art. no. 034005, doi: 10.1088/2053-1583/ab1764.

- [15] J. Kang, W. Liu, D. Sarkar, D. Jena, and K. Banerjee, "Computational study of metal contacts to monolayer transition-metal dichalcogenide semiconductors," *Phys. Rev. X*, vol. 4, no. 3, 2014, Art. no. 031005, doi: 10.1103/PhysRevX.4.031005.

- [16] Z. Cheng, Y. Yu, S. Singh, K. Price, S. G. Noyce, Y.-C. Lin, L. Cao, and A. D. Franklin, "Immunity to contact scaling in MoS<sub>2</sub> transistors using in situ edge contacts," *Nano Lett.*, vol. 19, no. 8, pp. 5077–5085, Jul. 2019, doi: 10.1021/acs.nanolett.9b01355.

- [17] J. Zhou, J. Lin, X. Huang, Y. Zhou, Y. Chen, J. Xia, H. Wang, Y. Xie, H. Yu, J. Lei, D. Wu, F. Liu, Q. Fu, Q. Zeng, C.-H. Hsu, C. Yang, L. Lu, T. Yu, Z. Shen, H. Lin, B. I. Yakobson, Q. Liu, K. Suenaga, G. Liu, and Z. Liu, "A library of atomically thin metal chalcogenides," *Nature*, vol. 556, no. 7701, pp. 355–359, 2018, doi: 10.1038/s41586-018-0008-3.

- [18] A. Jain, Á. Szabó, M. Parzefall, E. Bonvin, T. Taniguchi, K. Watanabe, P. Bharadwaj, M. Luisier, and L. Novotny, "One-dimensional edge contacts to a monolayer semiconductor," *Nano Lett.*, vol. 19, no. 10, pp. 6914–6923, Sep. 2019, doi: 10.1021/acs.nanolett.9b02166.

- [19] H. Choi, B. H. Moon, J. H. Kim, S. J. Yun, G. H. Han, S.-G. Lee, H. Z. Gul, and Y. H. Lee, "Edge contact for carrier injection and transport in MoS<sub>2</sub> field-effect transistors," ACS Nano, vol. 13, no. 11, pp. 13169–13175, Nov. 2019, doi: 10.1021/acsnano.9b05965.

- [20] Z. Yang, C. Kim, K. Y. Lee, M. Lee, S. Appalakondaiah, C. Ra, K. Watanabe, T. Taniguchi, K. Cho, E. Hwang, J. Hone, and W. J. Yoo, "A Fermi-level-pinning-free 1D electrical contact at the intrinsic 2D MoS<sub>2</sub>-metal junction," *Adv. Mater.*, vol. 31, no. 25, May 2019, Art. no. 1808231, doi: 10.1002/adma.201808231.

- [21] Y. Chai, R. Ionescu, S. Su, R. Lake, M. Ozkan, and C. S. Ozkan, "Making one-dimensional electrical contacts to molybdenum disulfidebased heterostructures through plasma etching," *Phys. Status Solidi*, vol. 213, no. 5, pp. 1358–1364, Jan. 2016, doi: 10.1002/pssa.201532799.

- [22] B. H. Moon, G. H. Han, H. Kim, H. Choi, J. J. Bae, J. Kim, Y. Jin, H. Y. Jeong, M.-K. Joo, Y. H. Lee, and S. C. Lim, "Junction-structure-dependent Schottky barrier inhomogeneity and device ideality of monolayer MoS<sub>2</sub> field-effect transistors," ACS Appl. Mater. Interface, vol. 9, no. 12, pp. 11240–11246, Mar. 2017, doi: 10.1021/acsami.6b16692.

- [23] T. Y. Hung, S.-Y. Wang, C.-P. Chuu, Y.-Y. Chung, A.-S. Chou, F.-S. Huang, T. Chen, M.-Y. Li, C.-C. Cheng, J. Cai, C.-H. Chien, W.-H. Chang, H.-S. P. Wong, and L.-J. Li, "Pinning-free edge contact monolayer MoS<sub>2</sub> FET," in *IEDM Tech. Dig.*, Dec. 2020, pp. 3.3.1–3.3.4, doi: 10.1109/IEDM13553.2020.9372028.

- [24] C.-H. Chu, H.-C. Lin, C.-H. Yeh, Z.-Y. Liang, M.-Y. Chou, and P.-W. Chiu, "End-bonded metal contacts on WSe<sub>2</sub> field-effect transistors," ACS Nano, vol. 13, no. 7, pp. 8146–8154, Jun. 2019, doi: 10.1021/acsnano.9b03250.

- [25] T. Schram, Q. Smets, B. Groven, M. H. Heyne, E. Kunnen, A. Thiam, K. Devriendt, A. Delabie, D. Lin, M. Lux, D. Chiappe, I. Asselberghs, S. Brus, C. Huyghebaert, S. Sayan, A. Juncker, M. Caymax, and I. P. Radu, "WS<sub>2</sub> transistors on 300 mm wafers with BEOL compatibility," in *Proc. 47th Eur. Solid-State Device Res. Conf. (ESSDERC)*, Sep. 2017, pp. 212–215, doi: 10.1109/ESSDERC.2017.8066629.

- [26] I. Asselberghs, Q. Smets, T. Schram, B. Groven, D. Verreck, A. Afzalian, G. Arutchelvan, A. Gaur, D. Cott, T. Maurice, S. Brems, K. Kennes, A. Phommahaxay, E. Dupuy, E. Radisic, J.-F. de Marneffe, A. Thiam, W. Li, K. Devriendt, C. Huyghebaert, D. Lin, M. Caymax, P. Morin, and I. Radu, "Wafer-scale integration of double gated WS2-transistors in 300 mm Si CMOS fab," in *IEDM Tech. Dig.*, Dec. 2020, pp. 40.2.1–40.2.4, doi: 10.1109/IEDM13553.2020.9371926.

- [27] A. D. Agyapong, K. A. Cooley, and S. E. Mohney, "Reactivity of contact metals on monolayer WS<sub>2</sub>," *J. Appl. Phys.*, vol. 128, no. 5, Aug. 2020, Art. no. 055306, doi: 10.1063/5.0014005.

- [28] D. Lin, X. Wu, D. Cott, D. Verreck, B. Groven, S. Sergeant, Q. Smets, S. Sutar, I. Asselberghs, and I. Radu, "Dual gate synthetic WS<sub>2</sub> MOSFETs with 120μS/μm Gm 2.7μF/cm<sup>2</sup> capacitance and ambipolar channel," in *IEDM Tech. Dig.*, Dec. 2020, pp. 3.6.1–3.6.4, doi: 10.1109/IEDM13553.2020.9372055.

- [29] X. Liu, J. Hu, C. Yue, N. Della Fera, Y. Ling, Z. Mao, and J. Wei, "High performance field-effect transistor based on multilayer tungsten disulfide," ACS Nano, vol. 8, no. 10, pp. 10396–10402, Oct. 2014, doi: 10.1021/nn505253p.

- [30] J. Kang, S. Tongay, J. Zhou, J. Li, and J. Wu, "Band offsets and heterostructures of two-dimensional semiconductors," *Appl. Phys. Lett.*, vol. 102, no. 1, 2013, Art. no. 012111, doi: 10.1063/1.4774090.

- [31] L. Cai, C. J. McClellan, A. L. Koh, H. Li, E. Yalon, E. Pop, and X. Zheng, "Rapid flame synthesis of atomically thin MoO<sub>3</sub> down to monolayer thickness for effective hole doping of WSe<sub>2</sub>," *Nano Lett.*, vol. 17, no. 6, pp. 3854–3861, Jun. 2017, doi: 10.1021/acs.nanolett. 7b01322.